Compreender o comportamento de circuitos digitais exige mais do que apenas conhecer portas lógicas. Exige uma compreensão de como os sinais mudam ao longo do tempo. Diagramas de tempo fornecem a linguagem visual para essa análise temporal. Eles mapeiam o estado de diversos sinais em relação a um clock ou a um evento específico. Para estudantes de ciência da computação, dominar esse conceito é essencial para projetar sistemas confiáveis.

Este guia explora a mecânica, técnicas de leitura e parâmetros críticos envolvidos em diagramas de tempo. Abordaremos tudo, desde transições de sinal básicas até violações complexas de tempo de setup e hold. Ao final deste resumo, você terá uma base sólida para analisar interações digitais.

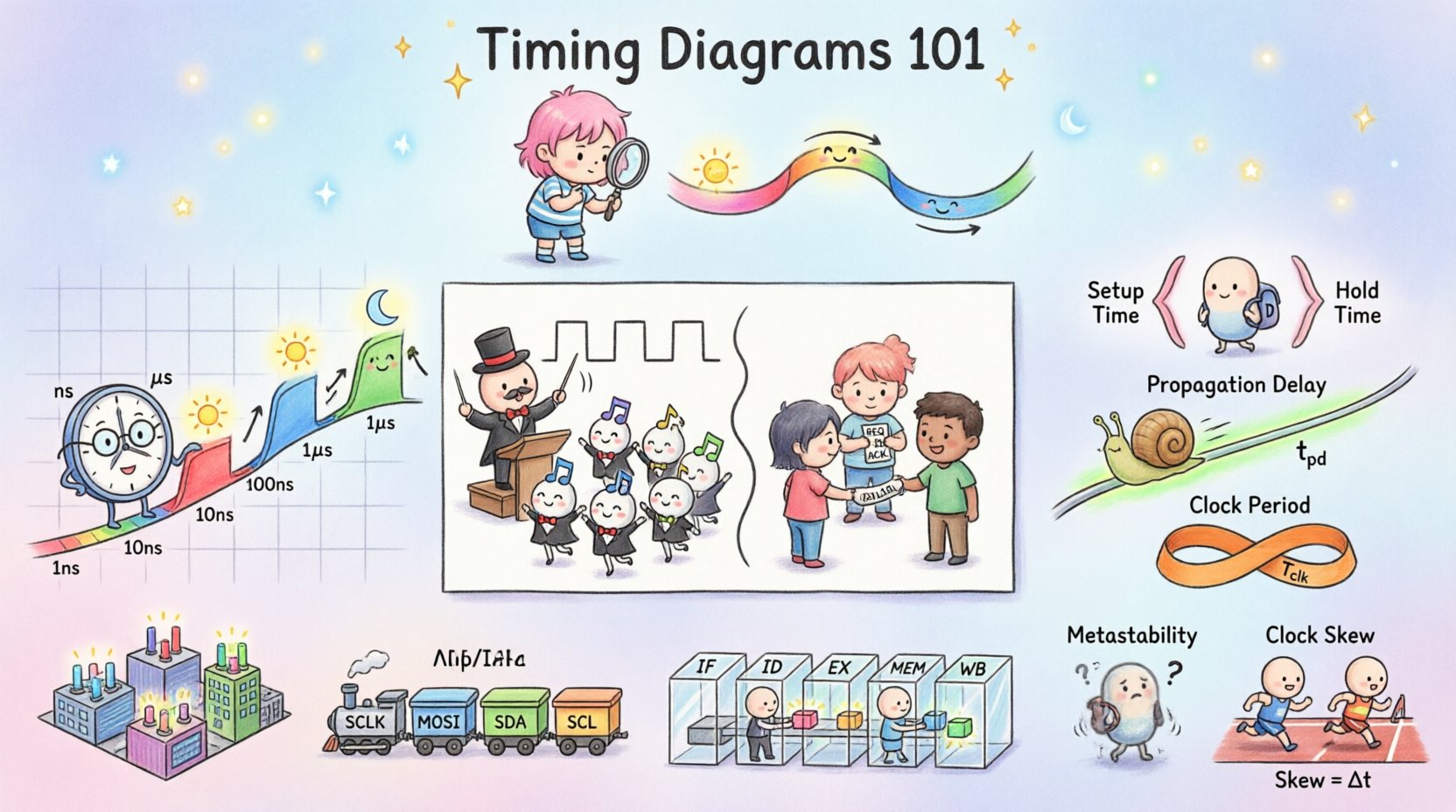

O que é um Diagrama de Tempo? ⏱️

Um diagrama de tempo é uma representação gráfica da relação entre dois ou mais sinais ao longo do tempo. Ele atua como uma linha do tempo para eventos digitais. Cada sinal é representado por uma linha horizontal. A posição vertical indica o nível lógico ou estado. O eixo horizontal representa a passagem do tempo.

Esses diagramas são vitais para verificar se um sistema digital opera corretamente. Eles ajudam engenheiros a prever como os dados se movem por registradores, barramentos e memória. Sem eles, depurar problemas de hardware torna-se quase impossível. Eles pontuam a lacuna entre a lógica abstrata e a realidade física.

Componentes Principais dos Sinais Digitais 📡

Antes de mergulhar nos diagramas, é necessário entender os próprios sinais. Sistemas digitais dependem de níveis de tensão para representar dados binários. Esses níveis nem sempre são estáticos; eles transitam entre estados.

- Nível Lógico Alto (1):Normalmente representa uma tensão próxima ao rail de alimentação.

- Nível Lógico Baixo (0):Normalmente representa uma tensão próxima ao terra.

- Transições (Edges): Os pontos de transição entre alto e baixo. As transições ascendentes vão de baixo para alto. As transições descendentes vão de alto para baixo.

- Estado Estável: O período em que um sinal permanece constante.

- Margens de Ruído: A tolerância que um sinal possui antes de ser mal interpretado.

Diagramas de tempo visualizam essas transições. Eles mostram exatamente quando um sinal muda e por quanto tempo permanece nesse estado. Essa precisão é crucial para garantir a integridade dos dados.

Compreendendo o Eixo do Tempo ⏳

O eixo horizontal é a base de qualquer diagrama de tempo. Ele representa a progressão do tempo. No projeto digital, esse eixo é frequentemente sincronizado com um sinal de clock. O clock atua como o coração do sistema.

As unidades no eixo do tempo variam de acordo com a velocidade do circuito. Unidades comuns incluem:

- Segundos (s):Usado para sistemas muito lentos.

- Milissegundos (ms):10^-3 segundos.

- Microsegundos (µs):10^-6 segundos.

- Nanosegundos (ns):10^-9 segundos. Padrão para processadores modernos.

- Picossegundos (ps):10^-12 segundos. Necessário para interfaces de alta velocidade.

Ao ler um diagrama, procure os marcadores de escala. Eles indicam a duração de cada ciclo. Isso ajuda a calcular atrasos de propagação e garantir que os sinais cheguem dentro da janela exigida.

Sistemas Síncronos vs Assíncronos 🔄

Sistemas digitais geralmente se dividem em duas categorias com base na forma como lidam com o tempo. Compreender essa diferença é essencial para desenhar diagramas precisos.

1. Sistemas Síncronos

Em designs síncronos, todas as mudanças de estado ocorrem em relação a um sinal de relógio global. O diagrama de tempo mostrará uma onda de relógio periódica. Cada flip-flop é atualizado na borda ativa desse relógio.

- Vantagens:Comportamento previsível. Mais fácil de verificar.

- Desafios:O atraso do relógio pode causar problemas se os sinais chegarem em tempos diferentes.

- Recursos do Diagrama:Linhas verticais frequentemente se alinham com as bordas do relógio para mostrar os momentos de captura.

2. Sistemas Assíncronos

Designs assíncronos não dependem de um relógio global. Em vez disso, usam protocolos de handshake ou sinais locais para acionar ações. Os diagramas de tempo aqui são mais irregulares.

- Vantagens:Consumo de energia mais baixo em alguns casos. Tempos médios de resposta mais rápidos.

- Desafios:Complexo de verificar. Suscetível a condições de corrida.

- Recursos do Diagrama:Os sinais acionam uns aos outros sem um ritmo fixo.

Parâmetros Críticos de Tempo 📏

Medidas específicas definem a confiabilidade de um diagrama de tempo. Esses parâmetros determinam se um circuito funcionará corretamente em todas as condições.

| Parâmetro | Descrição | Significância |

|---|---|---|

| Atraso de Propagação | Tempo necessário para um sinal viajar da entrada para a saída. | Limita a frequência máxima de operação. |

| Tempo de Preparação | Os dados devem permanecer estáveis antes da borda do clock. | Garante que o latch capture o valor correto. |

| Tempo de retenção | Os dados devem permanecer estáveis após a borda do clock. | Evita que o latch leia um valor em mudança. |

| Período do clock | Duração de um ciclo completo do sinal de clock. | Define a velocidade do sistema. |

| Ciclo de trabalho | Porcentagem do período em que o sinal está alto. | Afeta o consumo de energia e as margens de tempo. |

Aprofundamento: Tempo de preparação e tempo de retenção

Os tempos de preparação e retenção são as restrições mais críticas para a lógica sequencial. Se violados, o sistema pode entrar em um estado metastável, em que a saída é indefinida.

Violação do tempo de preparação: Isso ocorre quando os dados mudam muito perto da borda do clock. O circuito não tem tempo suficiente para se preparar para a captura. O resultado geralmente é um erro lógico.

Violação do tempo de retenção: Isso ocorre quando os dados mudam muito cedo após a borda do clock. O circuito ainda está tentando capturar o valor anterior. Isso geralmente é mais difícil de corrigir porque depende da disposição física.

Leitura e análise de diagramas 🔍

Analisar um diagrama de tempo exige uma abordagem sistemática. Siga estas etapas para interpretar os dados visuais com precisão.

- Identifique o clock: Encontre o sinal periódico. Este é o seu ponto de referência.

- Localize as bordas ativas: Determine se o sistema dispara nas bordas ascendentes ou descendentes.

- Trace as dependências dos sinais: Veja como as mudanças em um sinal afetam os outros.

- Verifique a presença de glitches: Procure pulsos curtos que possam ser ruído ou transições não intencionais.

- Verifique as restrições: Garanta que os tempos de preparação e retenção sejam respeitados para todos os registradores.

Considere um cenário simples de transferência de dados. Uma CPU envia dados para a memória. O diagrama de tempo mostrará as linhas de endereço estabilizando primeiro, seguidas pelas linhas de dados e, por fim, pelo sinal de escrita. Cada etapa deve ocorrer dentro de uma janela específica.

Violações Comuns e Seus Impactos ⚠️

Mesmo engenheiros com experiência enfrentam problemas de temporização. Compreender as violações comuns ajuda no diagnóstico de falhas.

1. Metastabilidade

Quando um sinal viola o tempo de setup ou hold, a saída do flip-flop pode oscilar antes de estabilizar. Esse estado é chamado de metastabilidade. Pode se propagar pelo sistema, causando comportamentos imprevisíveis. Circuitos de sincronização são frequentemente usados para mitigar esse risco.

2. Desvio

O desvio de clock ocorre quando o sinal de clock chega em componentes diferentes em momentos distintos. Isso pode reduzir a margem de temporização efetiva. O desvio positivo fornece mais tempo de setup, mas menos tempo de hold. O desvio negativo faz o oposto.

3. Condições de Corrida

As condições de corrida ocorrem quando a saída depende da sequência de eventos. Se dois sinais mudarem simultaneamente, a ordem de processamento determina o estado final. Diagramas de temporização ajudam a visualizar essas sequências para evitar corridas.

Aplicação na Arquitetura de Computadores 🖥️

Diagramas de temporização não são apenas ferramentas teóricas. São amplamente utilizados na arquitetura do mundo real.

Interfaces de Memória

DRAM e SRAM têm requisitos rigorosos de temporização. O controlador de memória deve esperar por atrasos específicos antes de ler ou escrever. Diagramas de temporização definem as sequências do barramento de comandos. Eles garantem que o banco de memória esteja pronto antes que os dados sejam acessados.

Protocolos de Barramento

Protocolos como I2C, SPI e UART dependem da temporização para comunicação. A linha de clock no SPI sincroniza a transferência de dados. No UART, a temporização baseia-se nas taxas de baud. O receptor deve amostrar a linha de dados exatamente no centro do período do bit. Um diagrama de temporização mostra a alinhamento do bit de início, bits de dados e bit de parada.

Estágios de Pipelining

Processadores modernos usam pipelining para executar múltiplas instruções ao mesmo tempo. Cada estágio deve ser concluído dentro de um ciclo de clock. Diagramas de temporização mapeiam o fluxo de dados pelos estágios de busca, decodificação, execução e escrita de retorno. Eles ajudam a identificar travamentos em que um estágio espera por outro.

Melhores Práticas para Documentação 📝

Criar diagramas de temporização claros garante que outros engenheiros possam entender seu projeto. Siga estas diretrizes para uma documentação eficaz.

- Use escalas consistentes: Garanta que o eixo do tempo seja uniforme em todo o documento.

- Rotule claramente: Nomeie todos os sinais. Evite rótulos genéricos como ‘Sinal 1’.

- Destaque as restrições: Use colchetes ou áreas sombreadas para mostrar as janelas de setup e hold.

- Agrupe sinais relacionados: Mantenha os sinais de controle juntos e os sinais de dados juntos.

- Inclua anotações: Adicione notas explicando transições complexas ou comportamentos especiais.

Considerações Avançadas 🔬

À medida que os sistemas ficam mais rápidos, a análise de temporização torna-se mais complexa. Vários fatores adicionam camadas de dificuldade.

1. Ruído na Fonte de Alimentação

Flutuações de tensão podem deslocar os níveis de limiar das portas lógicas. Isso altera efetivamente o atraso de propagação. Os diagramas de tempo devem considerar cenários de tensão mais desfavoráveis.

2. Variações de Temperatura

Componentes eletrônicos se comportam de forma diferente em temperaturas diferentes. Altas temperaturas aumentam a resistência e o atraso. Baixas temperaturas podem afetar a capacitância. Os projetistas devem verificar o tempo em toda a faixa de temperatura de operação.

3. Integridade do Sinal

Trilhas longas em uma placa de circuito atuam como linhas de transmissão. Reflexões e crosstalk podem distorcer os sinais. Os diagramas de tempo devem incluir diagramas de olho ou métricas de qualidade do sinal para links de alta velocidade.

Conclusão sobre a Análise de Tempo 🎯

Diagramas de tempo são o mapa para navegar na lógica digital. Eles traduzem estados binários abstratos em eventos físicos no tempo. Para um estudante de ciência da computação, a habilidade de ler e criar esses diagramas é uma competência fundamental.

Ao compreender ciclos de clock, atrasos de propagação e restrições de configuração, você pode projetar sistemas robustos e eficientes. A capacidade de visualizar o fluxo de sinal evita erros caros no design de hardware. À medida que a tecnologia avança, os princípios permanecem os mesmos. O tempo é a variável constante.

Concentre-se nos fundamentos. Pratique a leitura de diagramas existentes. Desenhe os seus próprios para cada novo circuito que construir. Essa disciplina será muito útil em sua carreira técnica.