No design digital moderno, compreender o fluxo de sinais ao longo do tempo é essencial para garantir a confiabilidade do sistema. Sistemas assíncronos, onde operações não são regidas por um único relógio global, apresentam desafios únicos em comparação com seus equivalentes síncronos. A principal ferramenta usada para visualizar e depurar essas interações complexas é o diagrama de tempo. Este guia oferece uma análise aprofundada sobre como construir, ler e analisar diagramas de tempo em ambientes assíncronos.

A Natureza do Design Assíncrono 🌐

Sistemas assíncronos operam sem um sinal de relógio centralizado que acione cada mudança de estado. Em vez disso, os eventos são disparados pelo término de operações anteriores ou pela chegada de dados. Essa abordagem oferece benefícios como consumo reduzido de energia e desempenho potencialmente maior em contextos específicos. No entanto, introduz complexidade em relação à sincronização de sinais e verificação de tempo.

Quando engenheiros analisam esses sistemas, devem levar em conta atrasos variáveis, tempos de propagação e a ausência de um ponto de referência universal. Os diagramas de tempo servem como a linguagem visual para mapear esses eventos. Eles permitem que equipes vejam a relação exata entre as transições de sinal ao longo do tempo.

Anatomia de um Diagrama de Tempo 📐

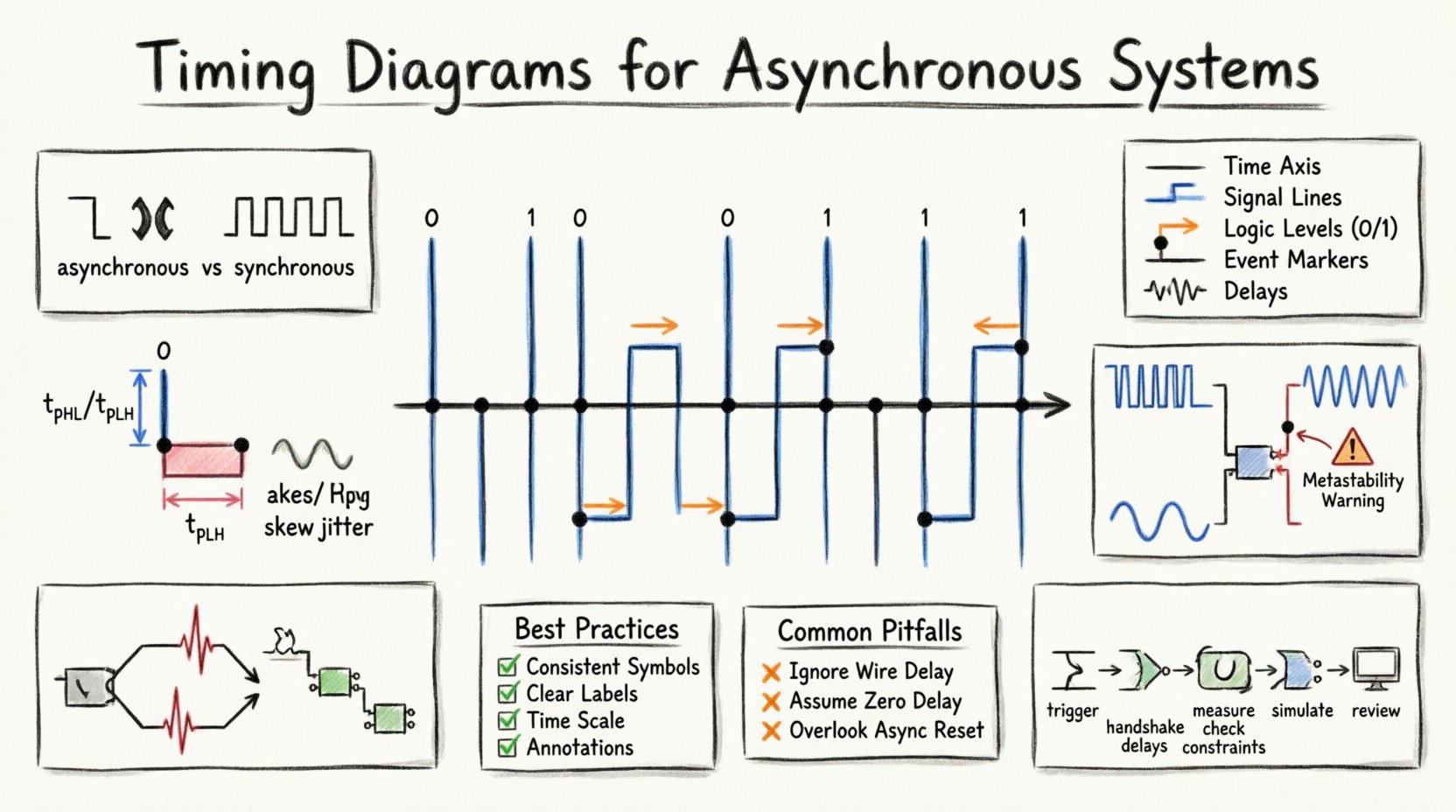

Um diagrama de tempo é uma representação gráfica do comportamento de sinais. Ele representa o tempo ao longo do eixo horizontal e os estados dos sinais ao longo do eixo vertical. Para analisar efetivamente um sistema assíncrono, é necessário compreender os componentes fundamentais que compõem esses diagramas.

- Eixo do Tempo: Representa a progressão do tempo. Na análise assíncrona, isso geralmente é relativo a um disparador de evento específico, e não a um ciclo de relógio.

- Linhas de Sinal: Linhas horizontais que representam fios ou redes individuais. Cada linha rastreia o nível lógico (Alto, Baixo ou Desconhecido) de um sinal específico.

- Níveis Lógicos: Geralmente indicados como

0(Baixo/Terra) e1(Alto/VCC). As transições entre esses estados são o cerne da análise. - Marcadores de Evento: Linhas verticais ou anotações que indicam ocorrências específicas, como uma mudança de estado em um sinal de handshake.

- Atrasos: Espaços visuais entre uma mudança de entrada e a mudança correspondente de saída, representando o atraso de propagação.

Diferentemente dos diagramas síncronos, que dependem de linhas de grade que representam bordas de relógio, os diagramas assíncronos dependem de fronteiras de eventos. Isso exige uma interpretação mais cuidadosa da distância entre as transições.

Parâmetros Críticos de Tempo ⚙️

Para analisar a integridade de um sistema assíncrono, parâmetros específicos de tempo devem ser medidos e comparados com as especificações do projeto. Esses parâmetros definem a janela em que um sinal deve permanecer estável para ser corretamente interpretado por um receptor.

Atraso de Propagação

O atraso de propagação é o tempo necessário para que um sinal percorra da entrada de um componente até sua saída. Na lógica assíncrona, esse atraso é uma fonte principal de incerteza. Variações na fabricação, temperatura e tensão podem alterar esse atraso.

- tpHL: Tempo necessário para que um sinal mude de Alto para Baixo.

- tpLH: Tempo necessário para que um sinal mude de Baixo para Alto.

- tpd: Atraso geral de propagação, frequentemente calculado como a média de tpHL e tpLH.

Ao analisar um diagrama de tempo, procure a distância horizontal entre a borda de entrada e a borda de saída resultante. Essa distância é o atraso de propagação.

Tempo de preparação e tempo de retenção

Mesmo em sistemas assíncronos, flip-flops e latchs frequentemente exigem janelas específicas de estabilidade. O tempo de preparação é a duração antes de um evento disparador em que os dados devem estar estáveis. O tempo de retenção é a duração após o evento disparador em que os dados devem permanecer estáveis.

Se essas janelas forem violadas, o sistema pode entrar em um estado de metastabilidade, em que a saída não é nem alta nem baixa, mas um nível de tensão indefinido. Diagramas de tempo ajudam a visualizar essas violações mostrando se os dados mudam muito perto de uma borda de controle.

Desvio e jitter

- S desvio: A diferença no tempo de chegada do mesmo sinal em dois pontos diferentes do circuito.

- Jitter: Variações de curto prazo no tempo do sinal. Em sistemas assíncronos, o jitter pode ser causado por ruído de alimentação ou acoplamento indesejado.

Manipulação de transições entre domínios de clock 🔄

Uma das fontes mais comuns de erros em sistemas mistos envolve transições entre diferentes domínios de clock. Mesmo que um sistema seja principalmente assíncrono, frequentemente contém sub-blocos síncronos operando em frequências diferentes. Diagramas de tempo são essenciais para verificar essas transições.

Quando um sinal passa de um domínio de clock para outro, o receptor pode amostrar o sinal em um momento em que o sinal está mudando. Isso leva à metastabilidade. A abordagem padrão para mitigar isso é usar um sincronizador, geralmente uma cadeia de flip-flops.

| Parâmetro | Descrição | Impacto no Diagrama de Tempo |

|---|---|---|

| Tempo de resolução de metastabilidade | Tempo necessário para que o sincronizador se estabilize em um nível lógico válido | Mostra um período estendido de estado indefinido antes que o sinal se estabilize |

| Latência entre domínios | Atraso adicional introduzido pelo sincronizador | Aumenta a diferença de tempo entre o evento de origem e o evento de destino |

| Latência de handshake | Tempo necessário para os sinais de confirmação em protocolos assíncronos | Cria um padrão de ida e volta no cronograma do sinal |

Os analistas devem garantir que o diagrama de tempo considere o tempo de resolução. Se um bloco posterior tentar ler o sinal antes que o sincronizador se estabilize, ocorre corrupção de dados.

Identificação e resolução de condições de corrida ⚠️

Uma condição de corrida ocorre quando o comportamento do sistema depende da timing relativa de eventos que não deveriam influenciar uns aos outros. Em lógica assíncrona, isso é uma preocupação frequente. Diagramas de tempo são o método principal para detectar essas condições.

Perigos estáticos

Um hazard estático ocorre quando um sinal deveria permanecer em um nível constante, mas momentaneamente muda devido a atrasos em caminhos. Por exemplo, se um sinal logicamente deveria permanecer em Alto, mas uma mudança na entrada causa uma breve queda para Baixo, isso é um hazard estático-1.

- Indicador Visual: Um pico estreito ou pulso em uma linha de sinal que deveria ser plana.

- Causa Raiz: Atrasos de propagação desiguais através de diferentes portas lógicas.

Hazard Dinâmicos

Hazard dinâmicos envolvem múltiplas transições quando apenas uma é esperada. Isso frequentemente acontece em caminhos lógicos complexos onde os sinais percorrem números diferentes de portas.

Passos de Análise para Condições de Corrida

- Trace os Caminhos: Identifique todos os caminhos que um sinal percorre da fonte até o destino.

- Meça os Atrasos: Calcule o atraso de cada caminho usando o diagrama de tempo.

- Compare as Bordas: Verifique se os tempos de chegada de sinais concorrentes se sobrepõem de forma que crie ambiguidade.

- Verifique a Estabilidade: Certifique-se de que os sinais de controle permaneçam estáveis durante a janela crítica de chegada de dados.

Se uma condição de corrida for encontrada, o projeto pode precisar ser reestruturado. Soluções comuns incluem adicionar buffers para equalizar atrasos, inserir protocolos de handshake ou usar estruturas FIFO assíncronas.

Integridade de Sinal e Considerações sobre Ruído 🔌

Diagramas de tempo não existem em um vácuo. A camada física introduz ruído que afeta a qualidade do sinal. Ao analisar sistemas assíncronos, engenheiros devem distinguir entre erros lógicos de tempo e degradação física do sinal.

Glitches de Sinal

Glitches são pulsos de curta duração que podem se propagar por um circuito. Em sistemas assíncronos, um glitch pode acionar incorretamente um latch ou flip-flop. Diagramas de tempo frequentemente mostram esses como picos finos.

- Filtragem: Certifique-se de que a lógica posterior tenha atraso suficiente para filtrar esses pulsos.

- Taxa de Borda:Bordas mais acentuadas (tempos de subida/queda mais rápidos) são mais suscetíveis à acoplamento de ruído.

Crosstalk

O crosstalk ocorre quando um sinal em um fio induz uma tensão em um fio adjacente. Isso pode deslocar o tempo de um sinal, fazendo com que chegue antes ou depois do esperado.

Em um diagrama de tempo, o crosstalk pode se manifestar como um deslocamento na localização da borda ou como um pico adicional de ruído. Para mitigar isso, o espaçamento entre sinais deve ser considerado na fase de projeto físico.

Melhores Práticas para Documentação 📝

Documentação clara garante que a análise de tempo possa ser reproduzida e compreendida por outros engenheiros. Um diagrama de tempo bem estruturado inclui metadados e anotações específicas.

Padronização

- Use símbolos consistentes para os níveis lógicos.

- Rotule todos os sinais claramente com sua função.

- Indique a escala de tempo explicitamente (por exemplo, nanossegundos por divisão).

Anotações

As anotações de texto são cruciais para explicar comportamentos específicos. Use setas para indicar transições críticas ou áreas potenciais de problema. Rotule os valores de atraso de propagação diretamente no diagrama.

Controle de Versão

Os diagramas de tempo evoluem conforme o projeto muda. Mantenha números de versão para todos os diagramas para garantir que a análise corresponda ao estado atual do hardware. Não dependa da memória para detalhes de tempo.

Processo de Análise Passo a Passo 🛠️

Para analisar efetivamente um sistema assíncrono, siga uma abordagem estruturada. Isso garante que nenhum parâmetro crítico de tempo seja negligenciado.

- Defina o Gatilho:Identifique o evento que inicia a sequência. Este é geralmente o ponto de partida para o eixo do tempo.

- Mapeie o Handshake:Rastreie os sinais de solicitação e confirmação. Certifique-se de que eles sigam o protocolo correto (por exemplo, handshake de quatro fases ou de duas fases).

- Meça os Atrasos:Calcule a latência total desde o gatilho até a saída final. Divida isso em atrasos de componentes.

- Verifique as Restrições:Verifique se os tempos de setup e hold são atendidos para todos os elementos de armazenamento envolvidos.

- Simule Variações:Analise o diagrama sob condições extremas, como temperatura máxima ou tensão mínima.

- Revise a Metastabilidade:Garanta que a probabilidade de metastabilidade seja reduzida a um nível aceitável por meio de sincronizadores.

Armadilhas Comuns na Análise de Tempo ⚡

Mesmo engenheiros experientes podem ignorar problemas sutis. Estar ciente das armadilhas comuns ajuda a evitar reprojetações custosas.

- Ignorar o Atraso de Fio:Contar apenas com o atraso da porta, negligenciando a resistência e a capacitância das interconexões.

- Assumindo Atraso Zero:Tratando os laços de feedback como instantâneos, o que é fisicamente impossível.

- Ignorando o Reset Assíncrono:Falhar em considerar o tempo dos sinais de reset em relação aos sinais de dados.

- Confundindo borda e nível: Confundindo comportamentos disparados por borda e disparados por nível na interpretação do diagrama.

Conclusão sobre a Verificação ✅

Diagramas de tempo são indispensáveis para a verificação de sistemas assíncronos. Eles fornecem uma representação visual concreta de relações de tempo abstratas. Ao analisar rigorosamente esses diagramas, engenheiros podem identificar condições de corrida, verificar protocolos de handshake e garantir a integridade do sinal.

A complexidade do design assíncrono exige precisão. Cada nanossegundo conta. Uma compreensão aprofundada dos atrasos de propagação, tempos de setup e tempos de hold permite a criação de sistemas robustos. Embora a ausência de um relógio global aumente a dificuldade, as insights obtidas com a análise detalhada de tempo levam a designs mais eficientes e confiáveis.

Continuar a aprimorar essas habilidades de análise garante que os sistemas funcionem corretamente sob condições ambientais variáveis. O objetivo é estabilidade e previsibilidade, alcançados por meio de documentação e medições meticulosas.

Considerações Avançadas 🔬

Para aplicações de alto desempenho, fatores adicionais entram em jogo. Isso inclui gradientes de temperatura ao longo do chip e queda de tensão durante eventos de comutação.

- Gradientes de Temperatura:Os sinais que viajam do centro quente de um chip até a borda mais fria experimentarão velocidades diferentes. Essa variação deve ser refletida na análise de tempo.

- Ruído na Rede de Alimentação:O ruído de comutação simultânea pode deslocar os limiares lógicos. Diagramas de tempo deveriam, idealmente, incluir uma representação da estabilidade da linha de alimentação.

- Latência Variável:Alguns protocolos assíncronos permitem latência variável. O diagrama de tempo deve mostrar a faixa de latências aceitáveis, e não apenas um único valor.

Ao incorporar essas considerações avançadas, a análise de tempo torna-se uma ferramenta abrangente para a validação do sistema. Ela vai além da verificação simples para uma otimização de desempenho verdadeira.

Lembre-se de que o tempo não é apenas sobre velocidade; é sobre correção. Um sistema rápido que falha devido a erros de tempo é menos útil do que um sistema mais lento que funciona de forma confiável. O diagrama de tempo é o mapa que o guia até essa confiabilidade.