No mundo intricado da engenharia embarcada, a precisão não é meramente uma preferência; é uma exigência. Os diagramas de tempo servem como o plano visual para compreender como os sinais interagem ao longo do tempo. Essas representações gráficas mapeiam níveis de tensão, ciclos de clock e transições de dados em relação a um eixo temporal. Para engenheiros que projetam microcontroladores, sensores ou interfaces de comunicação, dominar a leitura e a criação desses diagramas é essencial para garantir a confiabilidade do sistema.

Sem uma visão clara das relações temporais, os componentes de hardware podem falhar em se comunicar, levando à corrupção de dados ou travamentos do sistema. Este guia explora as aplicações práticas dos diagramas de tempo em diversos domínios dentro do desenvolvimento embarcado, oferecendo uma análise aprofundada de sua utilidade sem depender de ferramentas de software específicas.

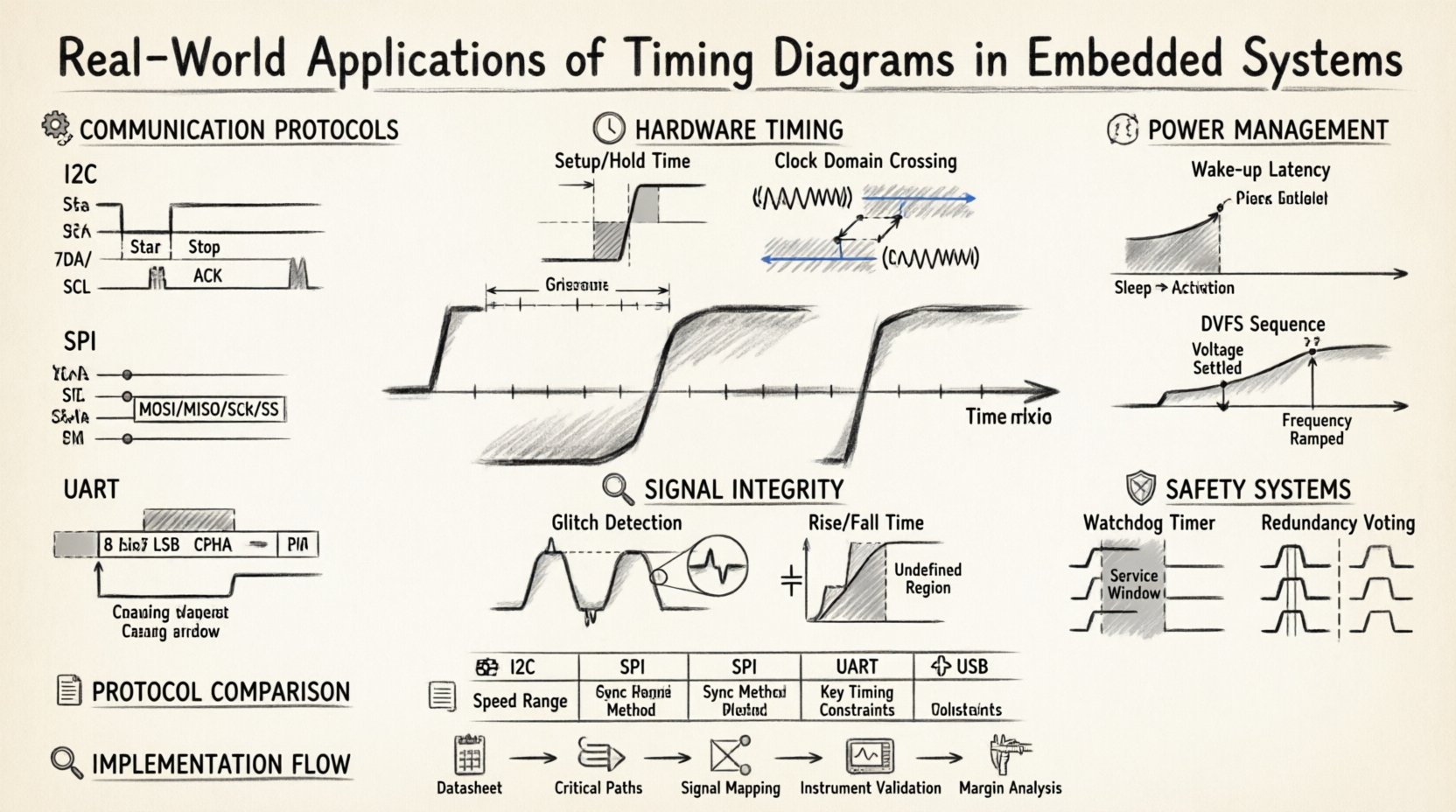

🔌 Análise de Protocolos de Comunicação

A comunicação serial é a base dos sistemas embarcados modernos. Os dados raramente permanecem em um único chip; eles se movem entre processadores, memória e periféricos. Os diagramas de tempo são essenciais para definir e verificar essas interações.

Circuito Inter-integrado (I2C)

O protocolo I2C utiliza uma interface de dois fios: Dados Série (SDA) e Relógio Série (SCL). Um diagrama de tempo para I2C revela a sequência específica necessária para a transmissão de dados.

- Condição de Início: A linha SDA passa de alta para baixa enquanto a linha SCL permanece alta. Isso sinaliza ao barramento para iniciar uma transação.

- Quadro de Endereço: O primeiro byte enviado contém o endereço de 7 bits do dispositivo-alvo mais um bit de leitura/escrita.

- Confirmação: O receptor puxa a linha SDA para baixa durante o nono pulso de clock para confirmar a recepção.

- Condição de Parada: A linha SDA passa de baixa para alta enquanto o SCL está alto, liberando o barramento.

Engenheiros usam esses diagramas para detectar problemas como estiramento de clock. Se um dispositivo escravo não conseguir processar os dados com rapidez suficiente, ele mantém a linha SCL baixa. O diagrama de tempo mostra essa extensão, permitindo que o projetista ajuste os loops de processamento ou os tamanhos dos buffers.

Interface Periférica Série (SPI)

O SPI é um protocolo síncrono frequentemente usado para comunicação de maior velocidade. Ele envolve quatro linhas: Saída do Mestre para Entrada do Escravo (MOSI), Entrada do Mestre para Saída do Escravo (MISO), Relógio Série (SCK) e Seleção do Escravo (SS).

- Polaridade do Relógio (CPOL): Determina o estado ocioso da linha de clock. É alta ou baixa antes do início dos dados?

- Fase do Relógio (CPHA): Define quando os dados são amostrados. É no primeiro ou no segundo flanco do clock?

- Temporização da Seleção do Chip: A linha SS deve permanecer baixa durante toda a duração da transação. Se ela apresentar um pulso alto, a transação é interrompida.

Compreender essas fases é vital. Uma discrepância entre CPOL ou CPHA entre mestre e escravo resulta em dados inválidos. Um diagrama de tempo visualiza esses flancos, tornando fácil identificar discrepâncias durante a inicialização do hardware.

Receptor/Transmissor Assíncrono Universal (UART)

Diferentemente de SPI e I2C, o UART não utiliza uma linha de clock. A sincronização depende das taxas de baud estabelecidas. Os diagramas de tempo aqui focam na duração do bit e no enquadramento.

- Bit de Início: Um pulso baixo indica o início de um byte.

- Bits de Dados: Tipicamente 8 bits, transmitidos com o bit menos significativo (LSB) primeiro.

- Bit de parada: Um pulso alto sinaliza o fim do byte.

Diagramas de tempo ajudam engenheiros a calcular a janela de tolerância. Se os relógios dos dois dispositivos se desviarem muito, o ponto de amostragem se desloca, causando erros. O diagrama ilustra a janela de amostragem, geralmente centralizada no meio do tempo do bit.

⏱️ Sincronização de Hardware e Tempos de Preparação

Além da comunicação, diagramas de tempo são indispensáveis para entender como portas lógicas e flip-flops interagem. A lógica digital depende de restrições de tempo precisas para funcionar corretamente.

Tempos de Preparação e Manutenção

Quando os dados entram em um registrador ou flip-flop, devem atender a requisitos específicos de tempo em relação à borda do relógio.

- Tempo de Preparação: A duração mínima em que os dados devem permanecer estáveisantesa borda do relógio chegar.

- Tempo de Manutenção: A duração mínima em que os dados devem permanecer estáveisdepoisa borda do relógio chegar.

Se um sinal violar o tempo de preparação, o registrador pode capturar um valor incorreto. Se violar o tempo de manutenção, pode ocorrer metastabilidade. Um diagrama de tempo visualiza o sinal de dados em relação à borda do relógio, destacando as zonas proibidas onde alterações nos dados não são permitidas.

Cruzamento de Domínio de Relógio (CDC)

Sistemas complexos frequentemente executam diferentes partes da lógica em frequências de relógio diferentes. Mover dados de um domínio de relógio rápido para um lento, ou vice-versa, introduz riscos.

- Sincronização: Usando uma cadeia de flip-flops para garantir que o sinal esteja estável antes de ser usado.

- Handshaking: Usando sinais de solicitação e confirmação para coordenar a transferência de dados sem um relógio compartilhado.

Um diagrama de tempo para CDC mostra a sequência de handshaking. Ele garante que os dados sejam válidos antes que o domínio receptor os reconheça. Isso evita perda de dados em transferências assíncronas.

🔍 Depuração e Integridade de Sinais

Quando um sistema embarcado se comporta de forma inesperada, diagramas de tempo são frequentemente o primeiro lugar onde os engenheiros procuram. Eles fornecem um registro histórico do comportamento dos sinais que testes estáticos não conseguem capturar.

Identificação de Glitches

Um glitch é um pulso breve e indesejado em uma linha de sinal. Pode durar apenas alguns nanossegundos, mas pode provocar uma mudança de estado em um flip-flop.

- Condições de Corrida:Ocorrem quando a ordem dos eventos importa e o tempo é muito apertado.

- Atraso de Propagação:Os sinais levam tempo para percorrer portas lógicas. Diagramas de tempo mostram esses atrasos claramente.

Ao sobrepor o diagrama de tempo esperado com os sinais reais capturados, engenheiros podem identificar exatamente onde ocorre a desvios. Isso permite correções direcionadas no firmware ou no projeto de hardware.

Margens de Ruído e Tempos de Subida/Queda

Sinais do mundo real não são ondas quadradas perfeitas. Eles apresentam tempos de subida e queda devido à capacitância e indutância nas trilhas.

- Tempo de Subida:O tempo necessário para um sinal passar do baixo para o alto.

- Tempo de Queda:O tempo necessário para um sinal passar do alto para o baixo.

Se essas transições forem muito lentas, o sinal pode passar muito tempo na região de tensão indefinida entre o nível lógico 0 e o nível lógico 1. Isso pode causar a geração de múltiplos bordas de clock ou erros lógicos. Um diagrama de tempo ajuda a medir essas inclinações para garantir que atendam às especificações do chip receptor.

💤 Gerenciamento de Energia e Estados de Baixo Consumo

A eficiência energética é uma preocupação principal em dispositivos embarcados alimentados por bateria. Diagramas de tempo desempenham um papel na otimização do consumo de energia.

Latência de Ativação

Quando um dispositivo entra em modo de suspensão, ele interrompe o clock para economizar energia. Acordar exige restaurar o clock e estabilizar a tensão.

- Tempo de Transição:O tempo necessário para passar do modo de suspensão para o estado ativo.

- Latência:O atraso entre um evento de acordar e o processador executar código.

Um diagrama de tempo da sequência de inicialização mostra o atraso entre o sinal de disparo e o clock do sistema se tornar estável. Essas informações são cruciais para aplicações em tempo real, onde um atraso de alguns milissegundos é relevante.

Escalonamento Dinâmico de Tensão e Frequência (DVFS)

Sistemas podem ajustar tensão e frequência com base na carga de trabalho. Diagramas de tempo ajudam a verificar as transições entre diferentes estados de desempenho.

- Rampa de Frequência:O clock muda suavemente ou abruptamente?

- Estabilização de Tensão:A tensão está estável antes da aplicação da nova frequência?

A sequência incorreta durante o DVFS pode causar quedas de tensão ou erros lógicos. O diagrama de tempo fornece a verificação de sequência necessária para garantir transições seguras.

🛡️ Sistemas Críticos para a Segurança

Em aplicações automotivas, médicas e industriais, a segurança é primordial. Diagramas de tempo são usados para verificar se os mecanismos de segurança funcionam dentro dos limites de tempo exigidos.

Temporizadores de Vigilância

Um temporizador de vigilância reinicia o sistema se o software travar. Diagramas de tempo definem o período de timeout.

- Período de Tempo Limite: O tempo máximo permitido entre reinícios.

- Janela de Serviço: O tempo que o software tem para reiniciar o temporizador.

Se a janela de serviço for muito longa, o watchdog pode ser acionado desnecessariamente. Se for muito curta, uma interrupção lenta pode causar uma reinicialização falsa. O diagrama garante que o tempo esteja alinhado com os requisitos de padrão de segurança.

Redundância e Votação

Alguns sistemas usam múltiplos processadores para votar sobre a saída correta. Diagramas de tempo garantem que todos os processadores alcancem a fase de votação simultaneamente.

- Sincronização: Todos os canais devem alinhar seus dados.

- Tempo Limite: Se um canal estiver atrasado, o sistema deve detectar a discrepância.

Isso é crítico em sistemas de controle de freio ou direção, onde um atraso pode ser perigoso. O diagrama de tempo mapeia a latência de cada canal para garantir que a lógica de votação funcione corretamente.

📋 Visão Geral da Comparação de Protocolos

A tabela a seguir resume as características principais de tempo de interfaces embarcadas comuns para auxiliar na seleção e no design.

| Protocolo | Faixa de Velocidade | Método de Sincronização | Caso de Uso Comum | Restrição de Tempo Importante |

|---|---|---|---|---|

| I2C | 100 kHz a 3,4 MHz | Relógio Compartilhado | Sensores, EEPROM | Estiramento de Relógio |

| SPI | 1 MHz a 50 MHz+ | Relógio Mestre | Memória Flash, Displays | Tempo de Setup do Seletor de Chip |

| UART | 9600 a 921600 bps | Assíncrono | Depuração, GPS, Bluetooth | Tolerância de Taxa de Baud |

| USB | 1,5 Mbps a 20 Gbps | Baseado em Pacotes | Periféricos, Armazenamento | Tempo de Token/Handshake |

🛠️ Etapas Práticas de Implementação

Criar um diagrama de tempo envolve uma abordagem sistemática. Começa com a compreensão da especificação e termina com a verificação.

- Revise os Datasheets:Cada componente possui uma seção de tempo. Procure pelas tabelas de características AC.

- Identifique os Caminhos Críticos: Determine quais sinais determinam a velocidade máxima do sistema.

- Mapeie as Dependências: Desenhe as relações entre os sinais. Qual deles dispara o outro?

- Valide com Instrumentos: Use analisadores lógicos ou osciloscópios para capturar formas de onda reais.

- Analise os Margens: Certifique-se de que há tempo suficiente entre os sinais para considerar variações de temperatura e tensão.

A documentação é essencial. Um diagrama de tempo bem anotado serve como referência para manutenção futura. Explica por que certos atrasos foram adicionados ou por que resistores de pull-up específicos foram escolhidos.

🚀 Considerações Avançadas

À medida que os sistemas se tornam mais complexos, a análise de tempo exige atenção mais aprofundada.

Jitter e Ruído de Fase

Os clocks não são perfeitamente estáveis. O jitter é a desvio da borda do clock em relação à sua posição ideal. Diagramas de tempo mostram a variação na posição da borda ao longo de múltiplos ciclos.

- Jitter de Período: Variação no período do clock.

- Jitter Ciclo a Ciclo: Variação de um ciclo para o próximo.

O jitter alto reduz as margens de setup e hold. Em interfaces de alta velocidade, como a memória DDR, isso pode levar a erros de leitura/escrita. Diagramas de tempo ajudam a quantificar esse jitter para garantir que permaneça dentro de limites aceitáveis.

Efeitos Térmicos

A temperatura afeta a velocidade dos transistores. À medida que um chip esquenta, os sinais ficam mais lentos.

- Análise do Pior Caso: Projete para a temperatura operacional máxima.

- Limitação Térmica: Garanta que o sistema não ultrapasse os limites térmicos seguros durante a operação de alta velocidade.

Um diagrama de tempo criado à temperatura ambiente pode não ser válido a 85°C. Os engenheiros devem levar em conta esses deslocamentos térmicos para garantir robustez.

📝 Pensamentos Finais

Diagramas de tempo são mais do que simples desenhos; são a linguagem da sincronização. Eles pontuam a lacuna entre a lógica teórica e a realidade física. Em sistemas embarcados, onde hardware e software se entrelaçam, uma compreensão clara do tempo dos sinais evita reprojetações custosas e garante confiabilidade.

Seja você depurando um protocolo de comunicação, otimizando o consumo de energia ou garantindo a segurança em um sistema crítico, esses diagramas fornecem a clareza necessária para tomar decisões informadas. Ao focar nos tempos de setup, atrasos de propagação e integridade do sinal, os engenheiros podem construir sistemas que funcionam de forma consistente em condições do mundo real.

O investimento em compreender as relações de tempo se traduz em estabilidade e desempenho. À medida que a tecnologia avança, os princípios permanecem os mesmos. O tempo é a constante, e dominar sua medição é a chave para um design embarcado bem-sucedido.