Sistemas digitais dependem de uma sincronização precisa para funcionar corretamente. Quando os sinais chegam na hora errada, ocorrem falhas lógicas, levando a um comportamento imprevisível. Compreender como analisar e corrigir esses problemas é essencial para qualquer pessoa que estuda lógica digital, engenharia de computadores ou eletrônica. Este guia aborda os conceitos fundamentais e os passos práticos para identificar e resolver problemas de temporização encontrados em circuitos sequenciais e na transmissão de dados.

Compreendendo Sinais de Relógio e Bordas ⏱️

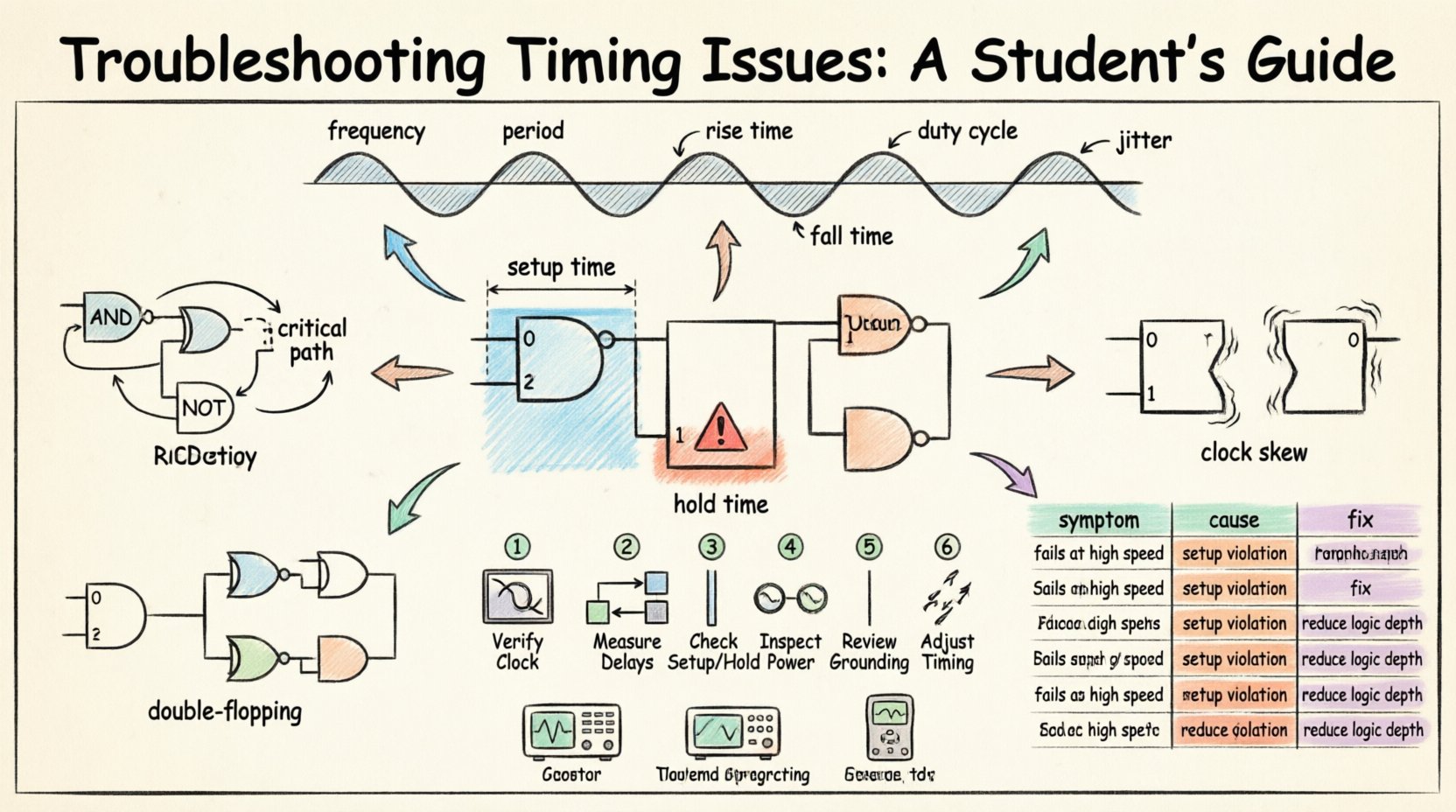

No centro da maioria dos projetos digitais encontra-se o sinal de relógio. Esta onda periódica determina quando os dados são amostrados e quando ocorrem mudanças de estado. A solução de problemas geralmente começa com a verificação da integridade deste sinal fundamental.

- Frequência e Período: A frequência do relógio determina a velocidade de operação. O período é a duração do tempo de um ciclo completo. Se o circuito exigir um relógio de 100 MHz, o período será de 10 nanossegundos. Qualquer desvio aqui afeta toda a lógica posterior.

- Tempos de Subida e Descida: Uma onda quadrada perfeita é teórica. Os sinais reais têm tempos finitos de subida e descida. Se a transição for muito lenta, o sinal pode passar muito tempo na região de tensão indefinida, causando múltiplas trocas ou erros lógicos.

- Ciclo de Trabalho: Este é a razão entre o tempo em que o sinal está alto em relação ao período total. Um ciclo de trabalho de 50% é o padrão, mas alguns projetos exigem ciclos assimétricos. Desvios podem distorcer as margens de temporização para requisitos de setup ou hold.

Ao inspecionar um circuito, use um osciloscópio ou analisador lógico para visualizar a forma de onda do relógio. Procure por picos de ruído, oscilações ou jitter excessivo. Jitter refere-se à desvios da borda do relógio em relação à sua posição ideal no tempo. Um jitter alto reduz a margem de temporização efetiva disponível para os dados se estabilizarem.

Violações de Tempo de Setup e Hold ⚠️

Essas são as violações de temporização mais comuns encontradas no projeto de lógica sequencial. Flip-flops e latchs têm requisitos específicos sobre quando os dados devem permanecer estáveis em relação à borda do relógio.

Tempo de Setup

O tempo de setup é a quantidade mínima de tempo antes da borda do relógio em que os dados devem estar estáveis. Se os dados mudarem muito perto da borda do relógio, o flip-flop pode não capturar o valor correto.

- A Restrição: O atraso de propagação da lógica combinacional que alimenta o flip-flop deve ser menor que o período do relógio menos o tempo de setup.

- O Sintoma: O sistema pode funcionar em frequências mais baixas, mas falhar à medida que a velocidade aumenta. Erros aleatórios de bits frequentemente ocorrem na saída.

- A Solução: Reduza a profundidade da lógica entre registradores, aumente o período do relógio ou use componentes mais rápidos.

Tempo de Hold

O tempo de hold é a quantidade mínima de tempo após a borda do relógio em que os dados devem permanecer estáveis. Se os dados mudarem muito cedo após a borda do relógio, o flip-flop pode perder o valor capturado.

- A Restrição: O atraso de propagação da lógica combinacional deve ser maior que o tempo de hold do flip-flop de destino.

- O Sintoma: As violações de hold frequentemente ocorrem independentemente da frequência. Isso porque o atraso é absoluto, não relativo ao período.

- A Solução: Adicione buffers de atraso na trajetória dos dados para reduzir a velocidade do sinal, ou redesenhe a lógica para reduzir o atraso.

É crucial distinguir entre esses dois. As violações de setup são dependentes da frequência, enquanto as violações de hold são dependentes do caminho. Um erro comum é tentar corrigir uma violação de hold diminuindo a velocidade do relógio; isso não funcionará e pode piorar ainda mais a situação.

Atrasos de Propagação e Análise de Caminho 📉

Os sinais não viajam instantaneamente. Cada fio, porta e componente introduz um atraso. Analisar esses atrasos é essencial para garantir que os dados cheguem a tempo.

- Atraso na Lógica Combinacional: Este é o tempo necessário para um sinal passar por portas como AND, OR e NOT. Cadeias longas de portas criam uma latência significativa.

- Atraso de Interconexão: Em uma placa física, os fios têm capacitância e resistência. Traços mais longos introduzem mais atraso. Isso geralmente é modelado como uma rede RC.

- Atraso de Pino para Pino: O tempo desde a entrada de clock até a saída de dados em um componente. Isso geralmente é especificado em folhas de dados.

Ao diagnosticar problemas, mapeie o caminho crítico. Este é o caminho com maior atraso entre dois elementos sequenciais. Se o caminho crítico exceder o período do clock, o projeto falhará. Para encontrá-lo, calcule a soma dos atrasos de todos os caminhos possíveis e identifique o máximo.

Desvio de Clock e Jitter 📶

Mesmo que a fonte de clock seja perfeita, o sinal pode chegar em componentes diferentes em tempos diferentes. Esse fenômeno é conhecido como desvio.

- Desvio de Clock: Isso ocorre quando o sinal de clock percorre distâncias diferentes para alcançar diferentes flip-flops. O desvio positivo atrasa o clock de captura, aliviando o tempo de setup, mas tornando mais rigoroso o tempo de hold. O desvio negativo torna mais rigoroso o tempo de setup, mas alivia o tempo de hold.

- Jitter de Clock: Variações de curto prazo no tempo de borda do clock. O jitter reduz o orçamento de tempo disponível para o setup de dados.

- Drift: Mudanças lentas na frequência do clock ao longo do tempo devido a variações de temperatura ou alimentação elétrica.

O desvio é geralmente gerenciado pela síntese da árvore de clock em projetos complexos. Em projetos acadêmicos, ele geralmente é minimizado roteando os traços de clock de forma uniforme e mantendo-os curtos. Se houver suspeita de desvio, meça o clock em múltiplos pontos do circuito simultaneamente.

Metastabilidade e Entradas Assíncronas 🌀

Quando os dados mudam no mesmo momento em que ocorre a borda do clock, um flip-flop entra em um estado metastável. Ele não se estabiliza imediatamente em 0 ou 1, mas permanece em um nível de tensão intermediário.

- O Risco:A metastabilidade pode se propagar pelo sistema, causando erros lógicos que são difíceis de reproduzir.

- Sinais Assíncronos:Entradas de interruptores externos ou portas de comunicação frequentemente não estão alinhadas com o clock interno. Essas devem ser sincronizadas.

- Duplo Flip-Flop:Uma técnica comum para resolver a metastabilidade é passar o sinal por dois flip-flops em série. O primeiro captura o estado metastável, e o segundo o resolve durante o próximo ciclo.

Trate sempre as entradas assíncronas como fontes potenciais de metastabilidade. Não as conecte diretamente a lógica que exige tempo rigoroso. Use circuitos de sincronização para garantir a transferência segura de dados entre domínios de clock diferentes.

Um Fluxo de Trabalho Passo a Passo para Diagnóstico 🛠️

Quando surge um problema de tempo, siga uma abordagem estruturada para isolar a causa. Alterações aleatórias têm poucas chances de produzir resultados.

- Verifique o Clock: Verifique a frequência, o ciclo de trabalho e a amplitude. Certifique-se de que o sinal seja estável e limpo.

- Medir atrasos:Use um analisador lógico para capturar os sinais de entrada e saída. Meça o atraso de propagação real do caminho.

- Verificar setup e hold:Calcule se o caminho atende às restrições de setup e hold com base nos atrasos medidos.

- Verificar alimentação:Quedas de tensão podem retardar as portas. Certifique-se de que a fonte de alimentação seja estável e forneça corrente suficiente.

- Revisar aterramento:Um aterramento ruim pode introduzir ruído que simula erros de tempo. Verifique laços de aterramento e caminhos de retorno compartilhados.

- Ajustar o tempo:Se o projeto for flexível, ajuste a frequência do clock ou adicione buffers para equilibrar o caminho.

A documentação é essencial durante este processo. Registre os sinais e medições. Esses dados ajudam a comparar o comportamento esperado com o desempenho real.

Tabela de Referência para Erros Comuns 📊

Use esta tabela como referência rápida para diagnosticar sintomas específicos.

| Sintoma Observado | Causa Provável | Ação Recomendada |

|---|---|---|

| O sistema falha em alta velocidade | Violação de tempo de setup | Reduza a profundidade lógica ou aumente o período do clock |

| O sistema falha em baixa velocidade | Violação de tempo de hold | Adicione buffers de atraso ao caminho de dados |

| Inversões aleatórias de bits | Ruído ou jitter no sinal | Verifique o blindagem e a estabilidade da fonte de alimentação |

| Saída trava ou reinicia | Metastabilidade | Implemente cadeias de sincronização |

| Comportamento inconsistente | Atraso de Relógio | Equilibre os comprimentos das trilhas do relógio |

| Nenhuma saída de forma alguma | Relógio não habilitado | Verifique os sinais de distribuição e habilitação do relógio |

Ferramentas e Instrumentação 📏

Embora as ferramentas de simulação sejam úteis, a verificação física frequentemente exige hardware específico. Compreender como usar corretamente esses instrumentos faz parte do conjunto de habilidades de solução de problemas.

- Osciloscópio:Essencial para visualizar níveis de tensão e forma do sinal. Use sondas de alta impedância para evitar sobrecarregar o circuito.

- Analizador Lógico:Melhor para sinais digitais. Ele captura o estado lógico (0 ou 1) ao longo do tempo. Pode disparar em padrões específicos para isolar erros.

- Contador de Frequência:Usado para verificar a frequência exata da fonte do relógio se um osciloscópio não estiver disponível.

Certifique-se de que as sondas estejam corretamente compensadas. Uma sonda não compensada pode distorcer a forma do sinal, levando a conclusões erradas sobre tempos de subida e atrasos.

Considerações Finais para Integridade de Sinal 🔒

Problemas de temporização são frequentemente sintomas de problemas mais amplos de integridade de sinal. À medida que os circuitos ficam mais rápidos, as propriedades físicas da placa tornam-se mais importantes.

- Crosstalk:Sinais em fios adjacentes podem interferir uns nos outros. Mantenha linhas de alta velocidade separadas das linhas sensíveis.

- Compatibilidade de Impedância: Se a impedância da trilha não corresponder ao driver ou receptor, ocorrem reflexões. Essas reflexões podem parecer atrasos de temporização.

- Efeitos Térmicos: À medida que os componentes esquentam, suas características elétricas mudam. Isso pode alterar os atrasos de propagação e levar a falhas de temporização sob carga.

Projetar para temporização exige uma visão holística. Não se trata apenas de portas lógicas; trata-se do meio físico pelo qual os sinais viajam. Ao seguir esses princípios, os alunos podem construir sistemas robustos que funcionam de forma confiável em diversas condições.

Prática regular com hardware real ajuda a internalizar esses conceitos. A teoria fornece a estrutura, mas a depuração prática desenvolve a intuição necessária para resolver problemas complexos de temporização de forma eficiente.