Цифровые системы полагаются на точную синхронизацию для правильной работы. Когда сигналы приходят в неподходящий момент, возникают сбои в логике, что приводит к непредсказуемому поведению. Понимание того, как анализировать и устранять эти проблемы, является необходимым для всех, кто изучает цифровую логику, компьютерную инженерию или электронику. Это руководство охватывает основные концепции и практические шаги для выявления и устранения проблем со временем, возникающих в последовательных схемах и передаче данных.

Понимание сигналов тактового генератора и их фронтов ⏱️

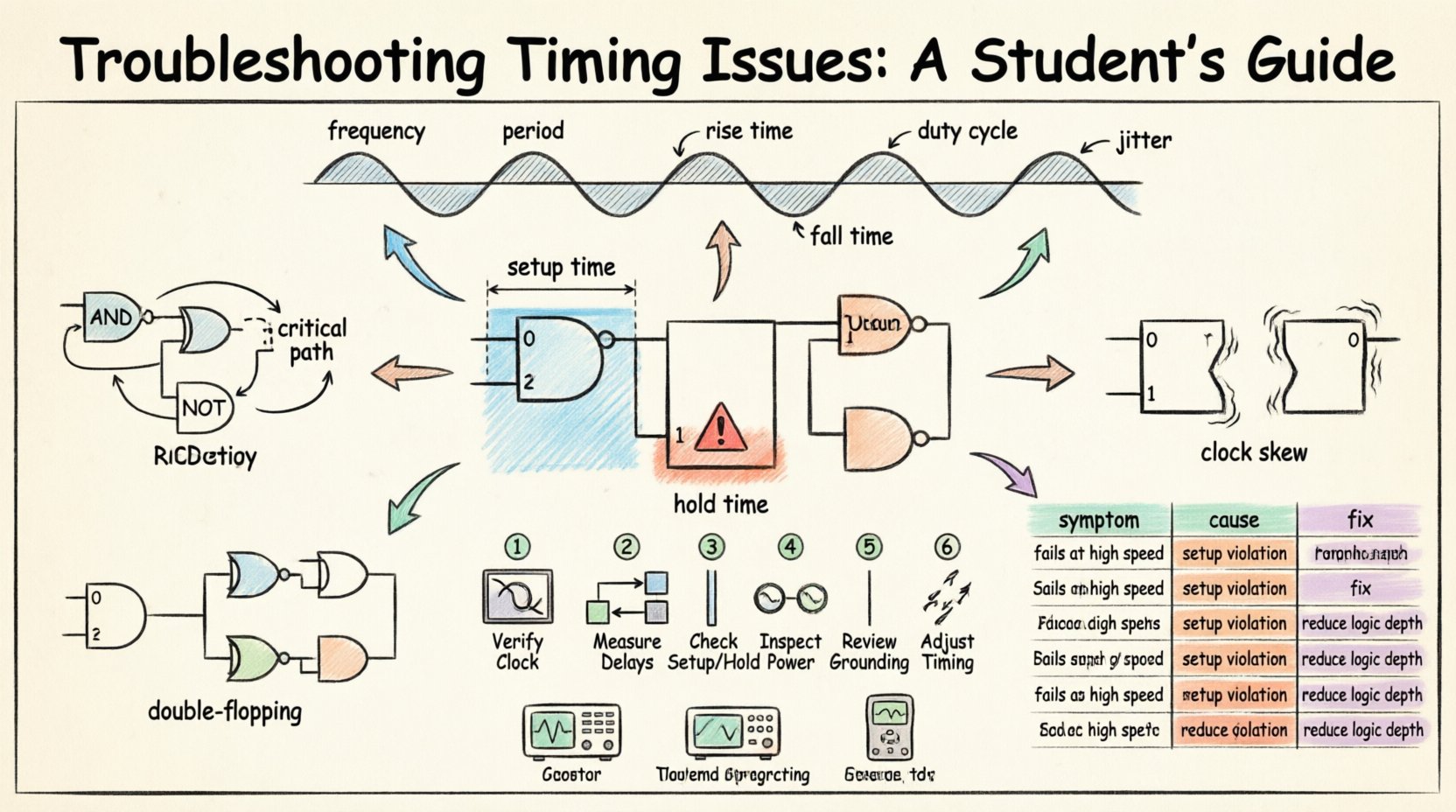

В центре большинства цифровых схем находится тактовый сигнал. Этот периодический сигнал определяет моменты выборки данных и изменения состояния. Устранение неисправностей часто начинается с проверки целостности этого фундаментального сигнала.

- Частота и период: Частота тактового сигнала определяет скорость работы. Период — это продолжительность одного полного цикла. Если схема требует тактового сигнала 100 МГц, период составляет 10 наносекунд. Любое отклонение здесь влияет на всю последующую логику.

- Время нарастания и спада: Идеальная прямоугольная волна — это теоретическое понятие. Реальные сигналы имеют конечное время нарастания и спада. Если переход слишком медленный, сигнал может слишком долго находиться в неопределенной зоне напряжения, что вызывает несколько переключений или ошибки логики.

- Цикл работы: Это отношение времени, в течение которого сигнал находится на высоком уровне, к общему периоду. Цикл 50% является стандартным, но некоторые схемы требуют асимметричных циклов. Отклонения могут нарушить временные интервалы для требований установки или удержания.

При проверке схемы используйте осциллограф или логический анализатор для просмотра формы тактового сигнала. Обратите внимание на шумовые всплески, колебания или чрезмерный джиттер. Джиттер — это отклонение фронта тактового сигнала от его идеального положения во времени. Высокий джиттер уменьшает эффективный временной интервал, доступный для стабилизации данных.

Нарушения времени установки и удержания ⚠️

Это наиболее распространенные нарушения временных параметров, встречающиеся при проектировании последовательной логики. Триггеры и защелки имеют определенные требования к моменту, когда данные должны быть стабильными относительно фронта тактового сигнала.

Время установки

Время установки — это минимальное время до фронта тактового сигнала, в течение которого данные должны быть стабильными. Если данные изменяются слишком близко к фронту тактового сигнала, триггер может не захватить правильное значение.

- Ограничение: Задержка распространения комбинированной логики, подающей сигнал на триггер, должна быть меньше, чем период тактового сигнала минус время установки.

- Симптом: Система может работать на низких частотах, но выходить из строя при увеличении скорости. На выходе часто возникают случайные ошибки битов.

- Решение: Уменьшите глубину логики между регистрами, увеличьте период тактового сигнала или используйте более быстрые компоненты.

Время удержания

Время удержания — это минимальное время после фронта тактового сигнала, в течение которого данные должны оставаться стабильными. Если данные изменяются слишком быстро после фронта тактового сигнала, триггер может потерять захваченное значение.

- Ограничение: Задержка распространения комбинированной логики должна быть больше времени удержания целевого триггера.

- Симптом: Нарушения времени удержания часто возникают независимо от частоты. Это связано с тем, что задержка является абсолютной, а не относительной к периоду.

- Решение: Добавьте буферы задержки в путь данных, чтобы замедлить сигнал, или перепроектируйте логику для уменьшения задержки.

Крайне важно различать эти два случая. Нарушения времени установки зависят от частоты, тогда как нарушения времени удержания зависят от пути. Распространённая ошибка — попытка устранить нарушение времени удержания путём замедления тактового сигнала; это не сработает и может усугубить ситуацию.

Задержки распространения и анализ пути 📉

Сигналы не распространяются мгновенно. Каждый провод, вентиль и компонент вносят задержку. Анализ этих задержек критически важен для обеспечения своевременного поступления данных.

- Задержка комбинаторной логики: Это время, необходимое для прохождения сигнала через вентили, такие как И, ИЛИ и НЕ. Длинные цепочки вентилей создают значительную задержку.

- Задержка межсоединений: На физической плате провода обладают емкостью и сопротивлением. Более длинные трассы вызывают большую задержку. Это часто моделируется как RC-сеть.

- Задержка от вывода к выводу: Время от входа тактового сигнала до выхода данных в компоненте. Обычно указывается в технических характеристиках.

При устранении неисправностей необходимо определить критический путь. Это путь с наибольшей задержкой между двумя последовательными элементами. Если критический путь превышает период тактового сигнала, проект не будет работать. Чтобы его найти, рассчитайте сумму задержек для всех возможных путей и определите максимальное значение.

Смещение тактового сигнала и джиттер 📶

Даже если источник тактового сигнала идеален, сигнал может прийти в различные компоненты в разное время. Это явление называется смещением.

- Смещение тактового сигнала: Это происходит, когда тактовый сигнал проходит разные расстояния до различных триггеров. Положительное смещение задерживает тактовый сигнал захвата, ослабляя время установки, но ужесточая время удержания. Отрицательное смещение ужесточает время установки, но ослабляет время удержания.

- Джиттер тактового сигнала: Кратковременные колебания времени фронта тактового сигнала. Джиттер уменьшает временной бюджет, доступный для установки данных.

- Дрейф: Постепенные изменения частоты тактового сигнала со временем из-за колебаний температуры или напряжения питания.

Смещение часто управляется синтезом тактовой сети в сложных проектах. В студенческих проектах оно обычно минимизируется за счёт равномерного прокладывания тактовых трасс и их укорачивания. Если подозревается смещение, измерьте тактовый сигнал одновременно в нескольких точках схемы.

Метастабильность и асинхронные входы 🌀

Когда данные изменяются одновременно с фронтом тактового сигнала, триггер переходит в метастабильное состояние. Он не сразу устанавливается в 0 или 1, а находится на промежуточном уровне напряжения.

- Риск: Метастабильность может распространяться по системе, вызывая логические ошибки, которые трудно воспроизвести.

- Асинхронные сигналы: Входные сигналы с внешних переключателей или портов связи часто не совпадают по времени с внутренним тактовым сигналом. Их необходимо синхронизировать.

- Двойная регистрация: Распространённый способ устранения метастабильности — прохождение сигнала через два триггера последовательно. Первый фиксирует метастабильное состояние, а второй устраняет его в следующем цикле.

Всегда рассматривайте асинхронные входы как потенциальные источники метастабильности. Не подключайте их напрямую к логике, требующей строгого соблюдения временных интервалов. Используйте синхронизирующие схемы для обеспечения безопасной передачи данных между различными тактовыми доменами.

Пошаговый процесс устранения неисправностей 🛠️

Когда возникает проблема с временными интервалами, придерживайтесь структурированного подхода для выявления причины. Случайные изменения вряд ли дадут результат.

- Проверьте тактовый сигнал: Проверьте частоту, цикл работы и амплитуду. Убедитесь, что сигнал стабилен и чист.

- Измерьте задержки:Используйте логический анализатор для захвата входных и выходных сигналов. Измерьте фактическую задержку распространения пути.

- Проверьте время установки и время удержания: Рассчитайте, удовлетворяет ли путь ограничениям времени установки и времени удержания на основе измеренных задержек.

- Проверьте питание: Падения напряжения могут замедлить работу вентилей. Убедитесь, что источник питания стабилен и обеспечивает достаточный ток.

- Проверьте заземление: Плохое заземление может вызвать шум, имитирующий ошибки времени. Проверьте наличие петель заземления и общих путей возврата.

- Настройте временные параметры: Если дизайн позволяет, измените частоту тактового сигнала или добавьте буферы для выравнивания пути.

Документирование имеет ключевое значение в этом процессе. Записывайте осциллограммы и измерения. Эти данные помогают сравнивать ожидаемое поведение с фактической производительностью.

Таблица распространённых ошибок 📊

Используйте эту таблицу как быстрое руководство для диагностики конкретных симптомов.

| Наблюдаемый симптом | Вероятная причина | Рекомендуемые действия |

|---|---|---|

| Система не работает на высокой скорости | Нарушение времени установки | Уменьшите глубину логики или увеличьте период тактового сигнала |

| Система не работает на низкой скорости | Нарушение времени удержания | Добавьте буферы задержки в путь данных |

| Случайные изменения битов | Шум сигнала или джиттер | Проверьте экранирование и стабильность источника питания |

| Выход зависает или сбрасывается | Метастабильность | Реализуйте цепочки синхронизаторов |

| Непостоянное поведение | Разница во времени тактирования | Выровняйте длины дорожек тактирования |

| Никакого выходного сигнала вообще | Тактирование не включено | Проверьте распределение тактового сигнала и сигналы разрешения |

Инструменты и измерительные приборы 📏

Хотя инструменты моделирования полезны, физическая проверка часто требует специального оборудования. Понимание правильного использования этих приборов является частью навыков устранения неисправностей.

- Осциллограф:Необходим для наблюдения уровней напряжения и формы сигнала. Используйте высоковольтные зонды, чтобы избежать нагружения цепи.

- Логический анализатор:Лучше подходит для цифровых сигналов. Он фиксирует логическое состояние (0 или 1) во времени. Может срабатывать на определённые паттерны для выделения ошибок.

- Частотомер:Используется для проверки точной частоты источника тактового сигнала, если осциллограф недоступен.

Убедитесь, что зонды правильно скомпенсированы. Нескомпенсированный зонд может искажать форму сигнала, что приводит к неверным выводам о времени нарастания и задержках.

Заключительные соображения по целостности сигнала 🔒

Проблемы с временной синхронизацией часто являются симптомами более широких проблем с целостностью сигнала. По мере того как схемы становятся быстрее, физические свойства платы имеют всё большее значение.

- Кросстолкинг:Сигналы на соседних проводах могут взаимно мешать. Держите высокоскоростные линии отделёнными от чувствительных линий.

- Согласование импеданса: Если импеданс дорожки не соответствует импедансу источника или приёмника, возникают отражения. Эти отражения могут выглядеть как задержки во времени.

- Тепловые эффекты: По мере нагрева компонентов их электрические характеристики изменяются. Это может изменить время распространения сигнала и привести к сбоям во времени при нагрузке.

Проектирование с учётом временных параметров требует комплексного подхода. Речь идёт не только о логических элементах, но и о физической среде, по которой передаются сигналы. Следуя этим принципам, студенты могут создавать надёжные системы, которые стабильно работают в различных условиях.

Регулярная практика с реальным оборудованием помогает усвоить эти концепции. Теория даёт основу, но практическое отладка формирует интуицию, необходимую для эффективного решения сложных проблем с временной синхронизацией.