В сложном мире встраиваемой инженерии время — всё. Микроконтроллер может идеально работать в симуляции, но катастрофически сбоить на аппаратном обеспечении из-за нескольких наносекунд задержки. Именно здесь диаграмма временных интервалов становится незаменимым инструментом. Эти визуальные представления отображают поведение сигналов во времени, предоставляя чёткое представление о том, как компоненты взаимодействуют в цифровой системе. Независимо от того, отлаживаете ли вы сбой в коммуникации или разрабатываете новый интерфейс периферийного устройства, понимание того, как читать и создавать диаграммы временных интервалов, является фундаментальным.

В этом руководстве рассматриваются основные принципы временной синхронизации сигналов — от базовых определений до сложных взаимодействий протоколов. Мы изучим, как интерпретировать волновые формы, строить точные диаграммы на основе измерительных данных и выявлять распространённые ошибки, приводящие к нестабильности системы. Освоив эти визуальные инструменты, вы получите возможность предсказывать поведение системы и проверять проекты до того, как они покинут рабочую станцию.

🔍 Понимание основ временной синхронизации сигналов

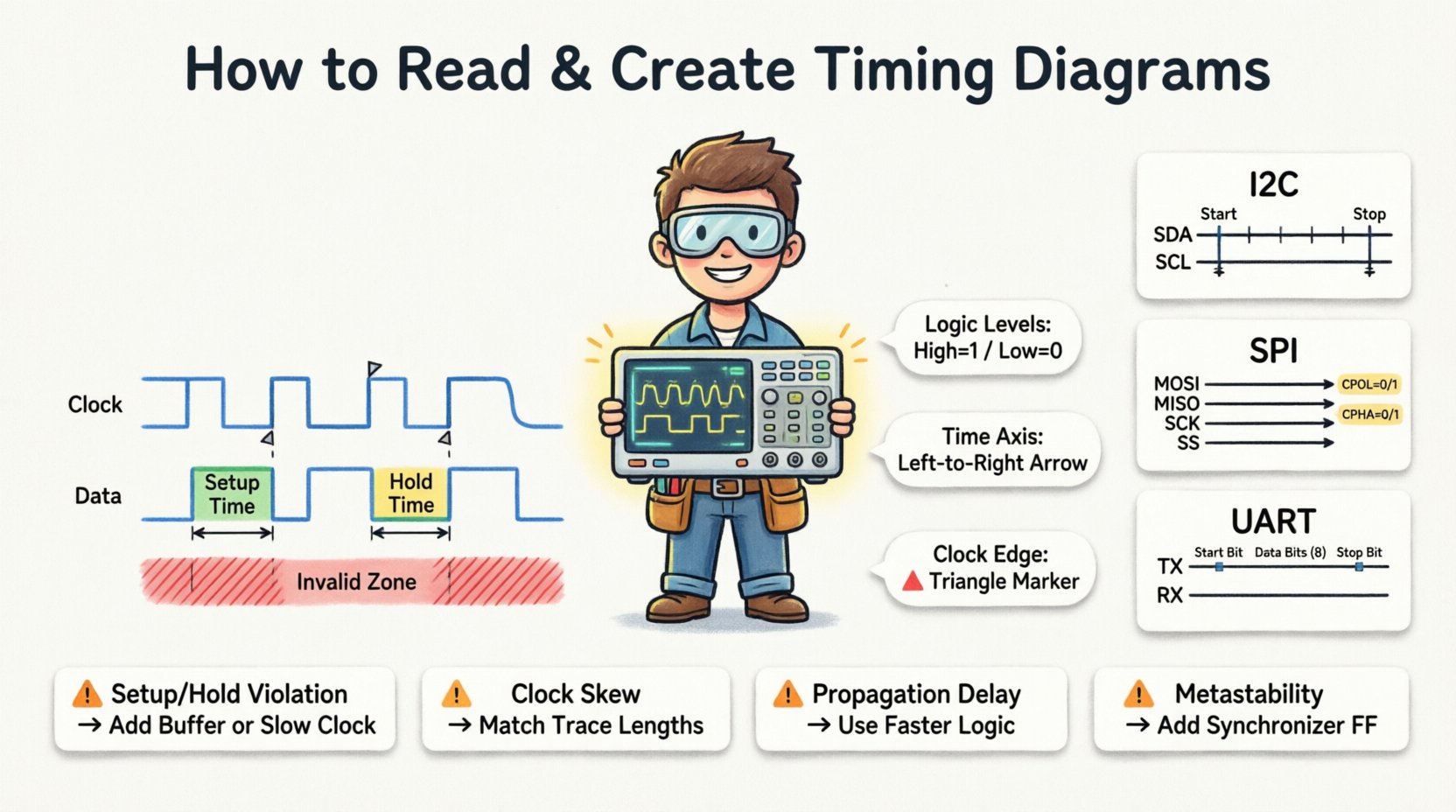

Диаграмма временных интервалов — это не просто рисунок; это математическое представление логических состояний относительно временной оси. В встраиваемых системах мы в основном работаем с цифровыми логическими уровнями, которые являются двоичными: Высокий (1) и Низкий (0). Однако сложность заключается как раз в переходах между этими уровнями.

- Логические уровни:Большинство встраиваемых систем работают на определённых пороговых значениях напряжения. Например, система на 3,3 В определяет высокий уровень как любое напряжение выше 2,0 В, а низкий — как любое напряжение ниже 0,8 В.

- Временная ось:Время течёт слева направо. Горизонтальное расстояние между элементами отражает продолжительность конкретных состояний или задержку между событиями.

- Сигнальные следы: Каждая горизонтальная линия представляет собой конкретный провод или шину. Несколько линий, расположенных вертикально друг над другом, позволяют сравнивать взаимосвязи между сигналами.

При анализе системы вы ищете причинно-следственную связь. Сигнал такта запускает изменение данных? Должен ли сигнал разрешения быть активным до того, как данные станут валидными? Диаграммы временных интервалов визуально отвечают на эти вопросы.

🛠️ Ключевые компоненты диаграммы временных интервалов

Чтобы правильно интерпретировать диаграмму, необходимо распознавать стандартные элементы, используемые для обозначения поведения сигнала. Эти компоненты определяют правила взаимодействия с аппаратным обеспечением.

| Компонент | Описание | Визуальный индикатор |

|---|---|---|

| Название сигнала | Определяет конкретный провод или шину | Текстовая метка слева |

| Логический уровень | Высокое (1) или низкое (0) состояние | Плоская горизонтальная линия вверху или внизу |

| Грань перехода | Переход от высокого к низкому или наоборот | Вертикальная линия, соединяющая уровни |

| Грань тактового сигнала | Точка срабатывания синхронной логики | Штриховая линия или маркер в виде треугольника |

| Зона недопустимых значений | Область, где данные нельзя прочитать | Заштрихованная или штрихованная область |

Понимание этих компонентов позволяет вам разобрать сложные взаимодействия. Например, заштрихованная область часто указывает на требование времени установки или удержания, когда приемное устройство не может надежно захватить данные.

👁️ Как читать диаграмму временных интервалов пошагово

Чтение диаграммы временных интервалов требует системного подхода. По сути, вы переводите визуальный паттерн в последовательность событий. Следуйте этому процессу, чтобы обеспечить точность.

1. Определите источник тактового сигнала

Большинство встроенных систем синхронны, то есть тактовый сигнал определяет темп операций. Найдите след тактового сигнала. Обычно он представляет собой регулярную, периодическую прямоугольную волну.

- Проверьте частоту. Это 1 МГц или 100 МГц? Это определяет скорость всей системы.

- Определите тип фронта. Устройство срабатывает по фронту повышения (с низкого на высокий) или по фронту понижения (с высокого на низкий)?

2. Определите окна действительности данных

Данные действительны только в определенных окнах относительно тактового сигнала. Обратите внимание на взаимосвязь между фронтом тактового сигнала и линией данных.

- Время установки: Данные должны оставаться стабильными в течение определенного периода до фронта тактового сигнала.

- Время удержания: Данные должны оставаться стабильными в течение определенного периода после фронта тактового сигнала.

Если данные изменяются в эти окна, возникает нарушение временных параметров, что приводит к метастабильности или неверному захвату данных.

3. Проанализируйте управляющие сигналы

Управляющие сигналы, такие как выбор микросхемы (CS), разрешение (EN) или сброс (RST), определяют, когда может происходить обмен данными.

- Выбор микросхемы активен по низкому уровню или по высокому уровню?

- Требуется ли активировать сигнал разрешения до начала переключения тактового сигнала?

- Есть ли асинхронные события, которые переопределяют логику тактового сигнала?

4. Проверьте механизмы согласования

Многие протоколы используют согласование для управления потоком данных. Обратите внимание на сигналы подтверждения (ACK) или готовности (RDY).

- Отправитель ждет сигнала перед передачей следующего байта?

- На диаграмме представлены условия таймаута?

📐 Как создавать точные диаграммы временных интервалов

Создание диаграммы временных интервалов так же важно, как и ее чтение. Она служит спецификацией для инженеров-конструкторов аппаратного обеспечения и руководством по проверке для разработчиков программного обеспечения. Вы можете генерировать их на основе требований, инструментов измерения или данных моделирования.

Шаг 1: Определите требования к протоколу

Прежде чем приступать к рисованию, соберите спецификации. Обычно они поступают из технического описания компонента, с которым вы взаимодействуете.

- Извлеките минимальную и максимальную частоты тактового сигнала.

- Запишите уровни напряжения для логических High и Low.

- Запишите ограничения по времени установки и удержания.

Шаг 2: Захват данных сигналов

Используйте аппаратные средства для захвата поведения в реальных условиях. Это гарантирует, что ваша диаграмма отражает реальность, а не теоретические идеалы.

- Осциллографы:Наилучшее решение для анализа целостности аналоговых сигналов и уровней напряжения.

- Логические анализаторы:Наилучшее решение для анализа переходов цифровых состояний и временных интервалов на нескольких каналах.

- Моделирование:Хорошо подходит для проверки логики до появления аппаратной части.

Шаг 3: Построение волновых форм

Рисуйте сигналы в хронологическом порядке. Убедитесь, что масштаб времени одинаков для всех каналов.

- Используйте прямые линии для логических уровней.

- Используйте диагональные линии для переходов, чтобы показать времена нарастания и спада.

- Обозначьте критические точки, такие как фронт тактового сигнала и изменение данных.

Шаг 4: Аннотирование критических ограничений

Аннотации предоставляют контекст, который визуальные изображения сами по себе не могут передать.

- Четко обозначьте окна времени установки и удержания.

- Укажите продолжительность конкретных состояний протокола (например, стартовый бит, стоп-бит).

- Выделите любые известные задержки или латентность в пути сигнала.

🌐 Диаграммы временных интервалов в распространённых встраиваемых протоколах

Разные протоколы связи имеют различные временные характеристики. Понимание этих нюансов крайне важно для интеграции.

1. Межинтегральная схема (I2C)

I2C — это двухпроводная синхронная последовательная шина. Она использует SDA (данные) и SCL (тактовый сигнал).

- Условие начала: SDA переходит от высокого уровня к низкому при высоком уровне SCL.

- Условие остановки: SDA переходит от низкого уровня к высокому, когда SCL находится на высоком уровне.

- Передача данных: Данные действительны, когда SCL находится на высоком уровне; изменения происходят, когда SCL находится на низком уровне.

- ACK/НACK: Приемник выводит SDA на низкий уровень во время девятого тактового импульса для подтверждения получения.

2. Последовательный периферийный интерфейс (SPI)

SPI — это четырехпроводная синхронная шина, обеспечивающая более высокую скорость по сравнению с I2C.

- Линии: MOSI (выход мастера), MISO (вход мастера), SCK (сигнал тактовой частоты), SS (выбор рабочего устройства).

- CPOL: Полярность тактового сигнала определяет состояние покоя (высокий или низкий уровень).

- CPHA: Фаза тактового сигнала определяет момент выборки данных (первый или второй фронт).

- Выбор микросхемы: Должен быть активирован (высокий уровень) до начала переключения тактового сигнала.

3. Универсальный асинхронный приемопередатчик (UART)

UART — асинхронный, что означает отсутствие общего сигнала тактовой частоты. Временные интервалы зависят от скорости передачи (скорости в бодах).

- Стартовый бит: Устанавливает линию на низкий уровень для сигнализации начала кадра.

- Биты данных: Передаются младшие биты первыми, обычно 8 бит.

- Стоп-бит: Устанавливает линию на высокий уровень для сигнализации окончания кадра.

- Четность: Дополнительный бит для проверки ошибок.

| Функция | I2C | SPI | UART |

|---|---|---|---|

| Часы | Синхронный (общий) | Синхронный (общий) | Асинхронный (без часов) |

| Провода | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| Адресация | Да (байтовая адресация) | Нет (основано на разводке) | Нет |

| Макс. скорость | ~400 кГц | ~50 МГц | ~3 Мбит/с |

⚠️ Распространенные нарушения временных интервалов и отладка

Даже при тщательном проектировании могут возникать нарушения временных интервалов. Часто они являются причиной случайных ошибок, которые трудно воспроизвести.

1. Нарушения времени установки и удержания

Это происходит, когда данные приходят слишком рано или слишком поздно относительно фронта тактового сигнала.

- Симптом: Повреждение данных или случайные ошибки при захвате логическим анализатором.

- Исправление: Уменьшите скорость тактового сигнала или оптимизируйте длины дорожек печатной платы.

2. Смещение тактового сигнала

Смещение тактового сигнала возникает, когда тактовый сигнал приходит к разным компонентам в разное время.

- Симптом: Гонки, при которых один триггер захватывает данные до того, как другой готов.

- Исправление: Выровняйте длины дорожек или используйте выделенную сеть распределения тактового сигнала.

3. Задержка распространения

Сигналы затрачивают время на прохождение через провода и вентили. Длинные следы добавляют значительную задержку.

- Симптом: Проблемы целостности сигнала или отражения на высокоскоростных линиях.

- Решение: Используйте резисторы терминации и делайте следы как можно короче.

4. Метастабильность

Когда асинхронные сигналы пересекают области тактовых частот, приемный триггер может перейти в метастабильное состояние.

- Симптом: Система зависает или происходит случайная перезагрузка.

- Решение: Используйте цепочки синхронизации (два или более триггера, соединенных последовательно), чтобы устранить сигнал.

📝 Лучшие практики документирования

Создание диаграмм временных интервалов для документации гарантирует, что будущие разработчики смогут понять систему, не прибегая к обратному проектированию аппаратной части.

- Согласованность: Используйте стандартные символы и стили линий во всех диаграммах проекта.

- Масштаб: Убедитесь, что ось времени линейна и четко обозначена с единицами измерения (нс, мкс, мс).

- Ссылка: Всегда связывайте диаграмму с конкретным разделом технического описания или стандартом протокола.

- Четкость: Избегайте перегруженности. Если сигнал статичен, отображайте его как горизонтальную линию, а не как колеблющиеся помехи.

- Версионирование: Обновляйте диаграммы каждый раз, когда существенно изменяется аппаратное или программное обеспечение.

🔗 Заключительные мысли о целостности сигнала

Диаграммы временных интервалов служат мостом между абстрактной логикой и физической реальностью. Они позволяют инженерам визуализировать невидимые ограничения цифровой электроники. Изучив, как их читать, вы сможете устранять сложные аппаратные неисправности. Изучив, как их создавать, вы сможете проектировать надежные системы, функционирующие надежно при любых условиях.

Процесс требует терпения и внимания к деталям. Каждый фронт, каждая задержка и каждый уровень напряжения имеют значение. По мере того как встраиваемые системы становятся быстрее и сложнее, зависимость от точных диаграмм временных интервалов будет только возрастать. Воспринимайте их как критически важные спецификации, а не как опциональную документацию.

Начните с анализа технических описаний используемых компонентов. Ищите спецификации по времени. Затем попробуйте нарисовать диаграммы на основе этих данных. Сравните свои рисунки с фактическими измерениями с помощью ваших инструментов. Этот цикл прогнозирования и проверки формирует интуицию, необходимую для проектирования высокого уровня встраиваемых систем.

Помните, что диаграмма — это инструмент коммуникации. Она должна передавать необходимую информацию другому инженеру с минимальной неоднозначностью. Четкие и точные диаграммы временных интервалов сокращают время разработки и предотвращают дорогостоящие изменения аппаратной части. Вложите время в освоение этого навыка, и он принесет пользу на протяжении всей вашей инженерной карьеры.