Понимание поведения сигналов во времени является основой цифровой электроники. Для студентов-инженеров овладение навыками интерпретации диаграмм временных интервалов — это не просто академическое упражнение, а критически важный навык при проектировании надежных систем. Эти визуальные представления отображают поведение сигналов по временной оси, раскрывая взаимосвязи между тактовыми циклами, валидностью данных и управляющими сигналами. Без прочного понимания этих методов даже простые схемы могут выйти из строя в реальных условиях.

В этом руководстве рассматриваются основные принципы, необходимые для эффективного чтения, создания и анализа диаграмм временных интервалов. Мы изучим механику синхронного и асинхронного проектирования, важность временных интервалов установки и удержания, а также способы избежания распространённых ошибок, приводящих к сбоям схем. К концу этой статьи у вас будет прочная основа для решения сложных задач цифровой логики.

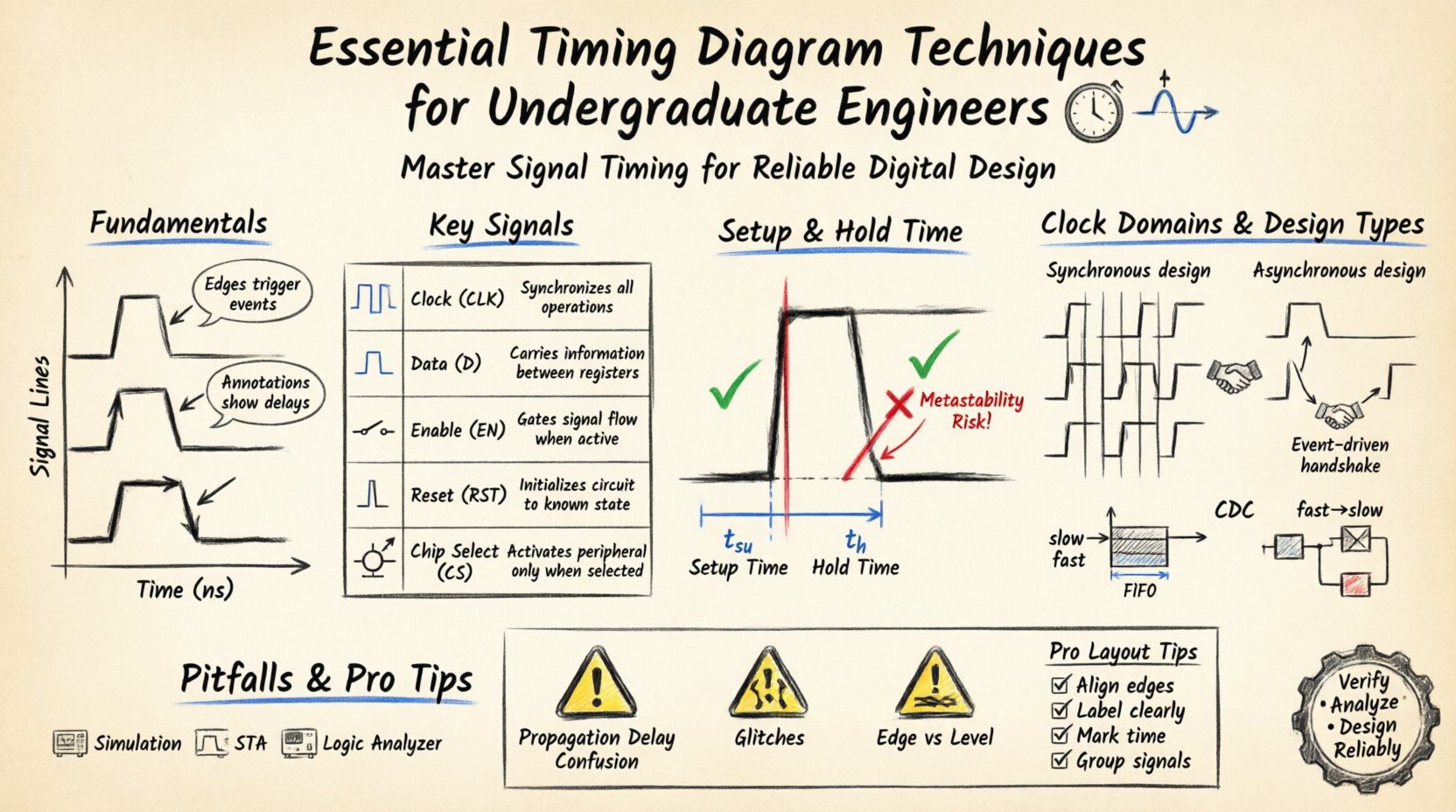

1. Основы диаграмм временных интервалов 📐

Диаграмма временных интервалов — это графическое представление сигналов во времени. Она позволяет инженерам визуализировать состояние различных линий в цифровой схеме. В отличие от логических схем, отображающих соединения, диаграммы временных интервалов показывают поведение. Они необходимы для отладки, проверки проектов и передачи информации о взаимодействии сигналов между аппаратными модулями.

Ключевые компоненты диаграммы временных интервалов

- Ось времени (X-ось):Обозначает ход времени. Обычно обозначается в наносекундах (нс) или тактовых циклах.

- Линии сигналов (Y-ось):Горизонтальные линии, представляющие отдельные провода или шины. Каждая линия соответствует определённому имени сигнала.

- Уровни логики:Сигналы обычно двоичные, обозначаются как Высокий (1) или Низкий (0). Иногда в схемах шин появляются состояния «Высокое сопротивление» (High-Z).

- Рёбра:Вертикальные переходы указывают на изменение состояния. Восходящие рёбра (с низкого на высокий) и нисходящие рёбра (с высокого на низкий) критически важны для запуска событий.

- Примечания:Текстовые метки часто указывают задержки, конкретные временные точки или условия, влияющие на сигнал.

Почему временные интервалы важны в цифровой логике

Цифровые системы зависят от точной синхронизации. Если сигнал приходит слишком рано или слишком поздно относительно тактового фронта, система может неправильно интерпретировать данные. Диаграммы временных интервалов делают эти ограничения видимыми. Они помогают ответить на вопросы, такие как:

- Данные стабильны ли до тактового фронта?

- Сколько времени занимает распространение сигнала через вентиль?

- Могут ли два тактовых сигнала из разных доменов мешать друг другу?

2. Ключевые сигналы и компоненты ⚡

Прежде чем анализировать сложные формы сигналов, необходимо распознавать стандартные сигналы, используемые в цифровой инженерии. Эти сигналы определяют, как перемещаются данные и когда они считаются валидными.

Распространённые типы сигналов

| Название сигнала | Функция | Типичное поведение |

|---|---|---|

| Тактовый сигнал (CLK) | Источник синхронизации | Регулярно импульсирует между 0 и 1 |

| Данные (D) | Носитель информации | Изменяет состояние в зависимости от входного сигнала или логики |

| Разрешение (EN) | Активирует модуль | Высокий уровень для разрешения работы, низкий уровень для отключения |

| Сброс (RST) | Инициализирует состояние | Импульс низкого или высокого уровня в начале |

| Выбор микросхемы (CS) | Выбирает устройство | Активный низкий уровень для адресации конкретного компонента |

Понимание активного состояния управляющих сигналов имеет решающее значение. Некоторые сигналы активны при высоком уровне, то есть работают при высоком напряжении. Другие активны при низком уровне, что обозначается чертой над названием (например, /СБРОС или RST_N), то есть работают при низком напряжении.

3. Анализ времени установки и удержания 🕒

Одним из наиболее важных аспектов анализа временных параметров является время установки и время удержания. Эти параметры определяют временной интервал, в течение которого данные должны быть стабильными относительно фронта тактового сигнала. Нарушение этих ограничений приводит к повреждению данных или метастабильности.

Время установки (tsu)

Время установки — это минимальная продолжительность, в течение которой данные должны оставаться стабильнымидоприхода активного фронта тактового сигнала. Если данные изменяются слишком близко к фронту тактового сигнала, триггер может не захватить правильное значение.

- Требование:Данные должны быть стабильными в течение tsu до фронта повышения.

- Последствия нарушения: Регистр может захватить неверные данные или перейти в неопределенное состояние.

Время удержания (th)

Время удержания — это минимальная продолжительность, в течение которой данные должны оставаться стабильнымипослеактивного фронта тактового сигнала. Флоп должен немного времени, чтобы зафиксировать значение, прежде чем придут новые данные.

- Требование:Данные должны оставаться стабильными в течение thпосле фронта.

- Последствия нарушения:Подобно нарушениям установки, это вызывает ошибки данных или метастабильность.

Визуализация времени установки и удержания

При чтении диаграммы временных интервалов ищите сигнал данных относительно фронта тактового сигнала. Линия данных должна быть плоской и неизменной в окне установки (до) и окне удержания (после). Если линия данных переключается в этих окнах, проект, скорее всего, содержит ошибки.

4. Пересечение областей тактирования ⏱️

В сложных системах различные части схемы могут работать с разными скоростями или частотами тактового сигнала. Передача данных между этими различными областями тактирования называется пересечением областей тактирования (CDC). Этот процесс вводит значительные временные сложности.

Типы областей тактирования

- Одинаковая частота, одинаковая фаза:Синхронный дизайн. Применяется простой анализ временных интервалов.

- Одинаковая частота, разная фаза: Требуются проверки выравнивания фаз.

- Разные частоты: Требуются методы синхронизации, такие как рукопожатие или буферы FIFO.

Обработка CDC на диаграммах временных интервалов

При анализе диаграмм с несколькими областями тактирования убедитесь, что четко различаете линии тактовых сигналов. Передача данных из медленной области в быструю может быть рискованной, если не управлять ею. Напротив, передача из быстрой в медленную может привести к потере данных, если приемник слишком быстро производит выборку.

- Протоколы рукопожатия: Используйте сигналы валидности/готовности для подтверждения завершения передачи данных.

- Буферы FIFO: Отделяют скорости производства и потребления.

- Синхронизаторы: Используйте многоступенчатые триггеры для снижения риска метастабильности.

5. Синхронный и асинхронный дизайн 🔄

Архитектура дизайна определяет, как выглядят диаграммы временных интервалов. Понимание различий помогает предсказать поведение сигнала.

Синхронный дизайн

Большинство цифровых логических схем синхронны. Все изменения состояния происходят на фронте центрального сигнала тактирования.

- Предсказуемость: Легче анализировать, поскольку временные параметры контролируются.

- Диаграммы временных интервалов: Регулярные, сетчатые узоры. Изменения данных совпадают с фронтами тактового сигнала.

- Ограничения: Задержка тактового сигнала может стать проблемой в крупных проектах.

Асинхронный дизайн

Изменения состояния происходят в зависимости от поступления сигналов, а не от глобального тактового сигнала. Это распространено в протоколах согласования и обработке прерываний.

- Гибкость: Может быть быстрее для конкретных задач, так как ждет только данных.

- Диаграммы временных интервалов: Нерегулярные. Сигналы зависят от предыдущих событий, а не от фиксированных временных интервалов.

- Риски: Подвержены гонкам и опасным ситуациям, если не спроектированы тщательно.

6. Распространённые ловушки и ошибки ❌

Даже опытные инженеры допускают ошибки при интерпретации или создании диаграмм временных интервалов. Знание этих распространённых ошибок может значительно сэкономить время отладки.

1. Пренебрежение задержкой распространения

Сигналы не изменяются мгновенно. Ворота имеют задержку распространения. Если вы рисуете диаграмму, предполагая мгновенные изменения, ваша симуляция не будет соответствовать реальности.

- Исправление: Всегда включайте значения задержек между переходами логики в ваших диаграммах.

2. Неправильная интерпретация сигналов с активным низким уровнем

Сигнал, помеченный как/CS активен при низком уровне. Если вы предположите, что он высокий, ваша логика будет инвертирована.

- Исправление:Проверьте техническое описание или схему на предмет активных состояний. Обратите внимание на круги на логических элементах.

3. Пропуск ложных импульсов

Ложные импульсы — это кратковременные, нежелательные импульсы. Они могут возникать, когда сигналы проходят по разным путям с различными задержками.

- Исправление:Используйте логику, свободную от опасностей, или добавьте этапы фильтрации в дизайн.

4. Смешение фронта и уровня

Некоторые схемы срабатывают по нарастающему фронту, другие — по спадающему фронту, а третьи — по уровню сигнала.

- Исправление:Проверьте условие срабатывания в спецификации компонента.

7. Чтение и создание профессиональных диаграмм 📝

Четкая коммуникация имеет решающее значение в инженерии. Хорошо выполненная временная диаграмма передает сложную информацию одним взглядом. Вот лучшие практики по созданию таких диаграмм.

Лучшие практики для компоновки

- Выравнивание краев:Убедитесь, что связанные сигналы изменяются с постоянными интервалами.

- Четкая маркировка:Используйте имена сигналов, а не просто общие линии.

- Обозначьте время:Укажите продолжительность циклов или конкретных задержек.

- Группировка сигналов:Сгруппируйте связанные сигналы (например, линии шины данных) вместе.

Пошаговый процесс создания

- Определите тактовые сигналы:Сначала нарисуйте линии тактовых сигналов. Они являются основой временной диаграммы.

- Добавьте управляющие сигналы:Разместите линии разрешения, сброса и выбора микросхемы.

- Нанесите данные:Добавьте линии данных на основе логического потока.

- Аннотируйте:Добавьте примечания по времени установки/удержания или конкретным задержкам.

- Обзор: Проверьте на нарушения и логическую согласованность.

8. Анализ реальных сценариев 🔍

Рассмотрим сценарий, связанный с операцией чтения памяти. Это распространенная задача для инженеров, работающих с микроконтроллерами.

Цикл чтения памяти

При чтении памяти процессор отправляет адрес, активирует команду чтения и ожидает данных.

- Шина адреса: Действителен до фронта тактового сигнала.

- Выбор чипа: Переходит в низкий уровень для активации памяти.

- Команда чтения: Переходит в низкий уровень для инициации передачи.

- Шина данных: Остается в состоянии высокого импеданса до тех пор, пока память не начнет его задействовать.

- Временные параметры: Данные должны быть стабильными до момента выборки процессором.

Рассмотрение целостности сигнала

По мере увеличения частоты целостность сигнала становится важным фактором. Отражения, кроссток и шум могут искажать формы сигналов. Диаграммы временных интервалов в высокоскоростных схемах должны учитывать эти проблемы физического уровня.

- Скорость нарастания: Насколько быстро происходит переход сигнала. Слишком быстрый переход вызывает шум; слишком медленный — ошибки временной синхронизации.

- Уровни напряжения: Убедитесь, что пороги логики соблюдены при изменении температуры и напряжения.

9. Расширенные концепции временных параметров 🧠

Для тех, кто хочет углубить свои знания, несколько расширенных концепций расширяют базовый анализ временных параметров.

Метастабильность

Метастабильность возникает, когда триггер не может установиться в устойчивое состояние 0 или 1 в требуемое время. Это обычно происходит, когда данные изменяются слишком близко к фронту тактового сигнала.

- Вероятность: Это вероятностное событие, а не детерминированное.

- Снижение риска: Используйте цепочки синхронизаторов (несколько триггеров последовательно), чтобы снизить вероятность до почти нуля.

Разница во времени прихода сигнала тактового генератора в различные части схемы

Разница во времени прихода сигнала тактового генератора в различные части схемы. Положительная разница (приходит позже) может помочь времени установки, но ухудшить время удержания. Отрицательная разница делает наоборот.

- Влияние на проектирование:Разница во времени прихода сигнала тактового генератора должна учитываться при составлении бюджета времени.

- Измерение:Используйте осциллографы или инструменты моделирования для измерения разницы во времени прихода сигнала тактового генератора.

Джиттер

Джиттер — это отклонение фронта тактового сигнала от его идеального положения. Он уменьшает эффективные временные интервалы установки и удержания.

- Типы:Джиттер периода, джиттер цикл-к-циклу и случайный джиттер.

- Влияние:Высокий джиттер ограничивает максимальную рабочую частоту системы.

10. Инструменты и методологии 🛠️

Хотя ручной анализ полезен для обучения, современная инженерия полагается на инструменты. Однако именно понимание базовой теории позволяет эффективно использовать эти инструменты.

Программное обеспечение моделирования

Языки описания аппаратных средств (HDL) позволяют проводить моделирование. Эти инструменты автоматически генерируют диаграммы временных интервалов из кода. Вам необходимо понимать результат, чтобы проверить правильность кода.

Статический анализ временных характеристик (STA)

Инструменты статического анализа временных характеристик математически проверяют, что все пути соответствуют требованиям по времени, без необходимости моделирования. Они проверяют нарушения времени установки и удержания во всех условиях (температура, напряжение).

Отладка с помощью логических анализаторов

Аппаратные отладчики фиксируют реальные сигналы с платы. Они отображают диаграммы временных интервалов, соответствующие реальности, помогая выявить проблемы на физическом уровне, которые могут быть пропущены при моделировании.

Заключение 🏁

Диаграммы временных интервалов — это язык поведения цифровых сигналов. Они служат мостом между абстрактной логикой и физической реальностью. Для студентов-инженеров вложение времени в освоение этих методов окупается на протяжении всей карьеры. Независимо от того, проектируете ли вы простой счётчик или сложный процессор, способность читать и анализировать временные ограничения является обязательной.

Фокусируясь на времени установки и времени удержания, понимая области тактовых сигналов и избегая распространённых ошибок, вы создаёте прочную основу. Помните, что всегда нужно проверять активные состояния и учитывать задержки распространения. По мере продвижения вы столкнётесь с более сложными сценариями, но основные принципы остаются неизменными. Продолжайте практиковаться в анализе диаграмм, и ваши проекты станут более надёжными и эффективными.

Продолжайте совершенствовать свои навыки, изучая спецификации и анализируя реальные формы сигналов в схемах. Область цифровой инженерии быстро развивается, но основы анализа временных характеристик остаются неизменными.