Цифровые системы полагаются на точную синхронизацию для правильной работы. Без точного временного управления повреждение данных, сбои системы и аварии становятся неизбежными. Диаграмма временных интервалов предоставляет визуальное представление о том, как сигналы изменяются во времени, обеспечивая четкое понимание взаимосвязей между циклами тактового сигнала, действительностью данных и управляющими сигналами. В этом руководстве рассматривается важная роль диаграмм временных интервалов в различных отраслях, приводятся практические примеры и технические решения для типичных проблем.

🔍 Понимание основ

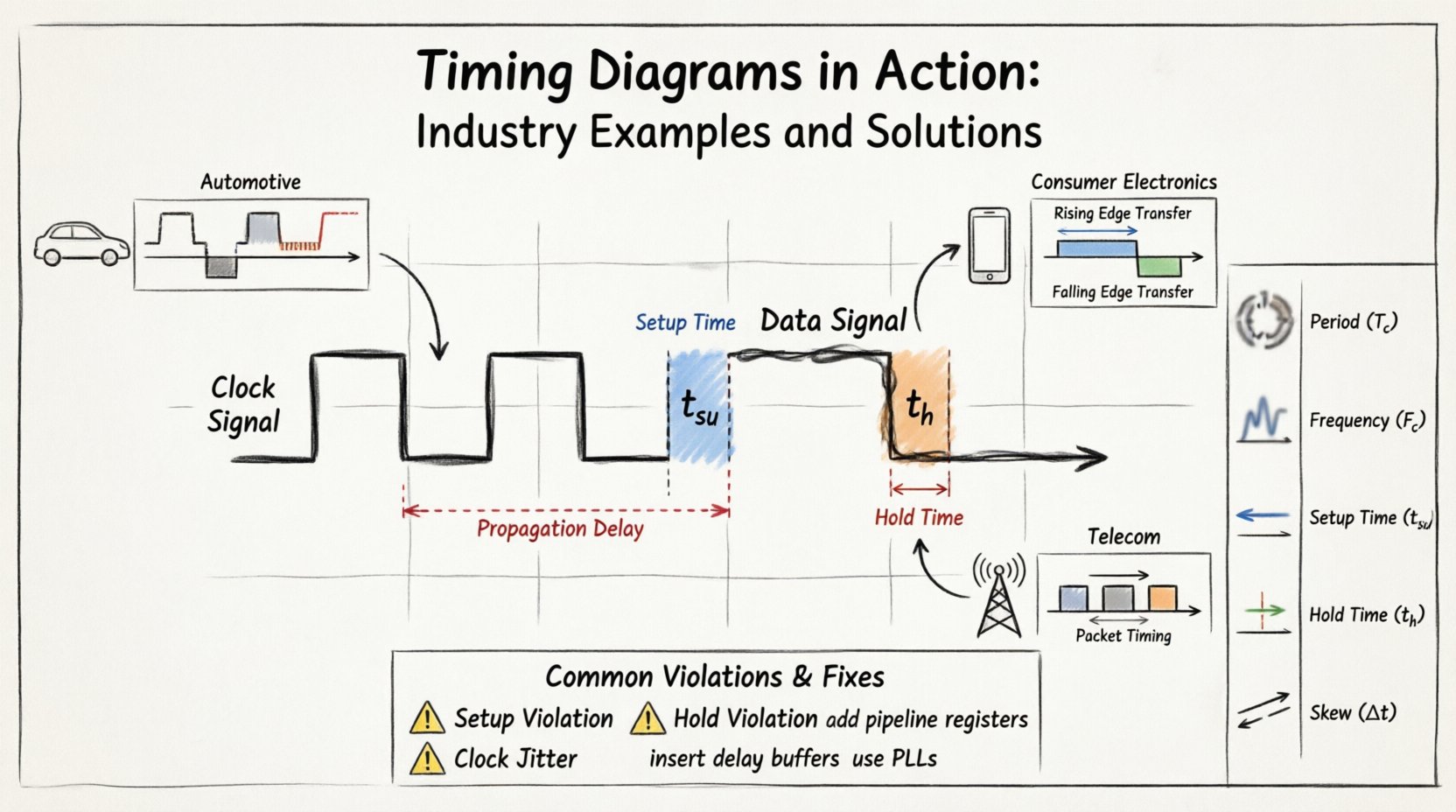

Прежде чем приступать к конкретным приложениям, необходимо понять основные компоненты диаграммы временных интервалов. Эти диаграммы отображают поведение сигналов относительно опорного тактового сигнала. Это не просто рисунки; это математические ограничения, определяющие поведение аппаратных средств.

- Гребни сигнала: Переход от низкого уровня к высокому (нарастающий фронт) или от высокого к низкому (спадающий фронт) вызывает смену состояния в последовательной логике.

- Период тактового сигнала: Продолжительность между двумя последовательными фронтами одного и того же типа определяет доступное время для стабилизации логики.

- Задержка распространения: Время, необходимое для прохождения сигнала от входного вывода к выходному через логические элементы.

- Время установки и время удержания: Критические ограничения, обеспечивающие стабильность данных до и после тактового фронта.

Когда эти параметры нарушаются, цепь может перейти в метастабильное состояние, что приводит к непредсказуемому поведению. Инженеры используют диаграммы временных интервалов для проверки того, что физическая реализация проекта соответствует этим логическим требованиям.

🚗 Автомобильная электроника: критически важное время

Автомобильная промышленность требует максимального уровня надежности. В автомобилях содержится десятки электронных блоков управления (ЭБУ), обменивающихся данными по шинам, таким как CAN (сеть управления контроллерами), LIN (локальная межсоединительная сеть) и FlexRay. Анализ временных интервалов здесь важен не только для скорости, но и для детерминизма и безопасности.

1. Арбитраж шины CAN

Шина CAN позволяет нескольким узлам обмениваться данными по одному проводу. Диаграмма временных интервалов для арбитража CAN показывает, как определяется приоритет при конфликте на шине.

- Доминирующий против резервного: Логические уровни представлены состояниями напряжения. Бит с доминирующим уровнем (0) подавляет бит с резервным уровнем (1).

- Синхронизация: Узлы синхронизируются с началом бита кадра с помощью сегментов синхронизации.

- Точка выборки: Данные выбираются в определённой доле времени бита, чтобы избежать шумов.

Если точка выборки слишком близка к краю, шум может вызвать ошибки битов. Если она слишком поздняя, данные могут быть нестабильными. Диаграммы временных интервалов помогают инженерам правильно установить точку выборки, обычно около 80% времени бита.

2. Выборка АЦП при объединении данных с датчиков

Современные автомобили используют несколько датчиков (радар, лидар, камеры), чтобы создать представление об окружающей среде. Аналого-цифровые преобразователи (АЦП) должны производить выборку сигналов с точными интервалами, чтобы избежать эффекта наложения.

- Джиттер тактового сигнала: Колебания времени тактового фронта вносят шум в цифровой сигнал.

- Задержка: Время от входа сигнала с датчика до выхода обработанных данных должно быть минимизировано для управления в реальном времени.

- Перемежение:Часто несколько АЦП работают параллельно. Диаграммы временных интервалов обеспечивают выравнивание их фаз, чтобы предотвратить пропуски данных.

📱 Электроника для потребителей: высокоскоростные интерфейсы

Потребительские устройства ориентируются на производительность и энергоэффективность. Интерфейсы, такие как память DDR и интерфейсы дисплеев, требуют строгих временных окон для достижения высокой пропускной способности без увеличения потребления энергии.

1. Интерфейсы памяти DDR

Память с двойной скоростью передачи (DDR) передает данные как на восходящем, так и на нисходящем фронтах тактового сигнала. Это удваивает эффективную скорость передачи данных, но вдвое сокращает временной интервал для стабильности данных.

| Параметр | Определение | Последствия нарушения |

|---|---|---|

| Время установки | Время, в течение которого данные должны быть стабильными до тактового фронта | Пропущенная передача данных, зависание системы |

| Время удержания | Время, в течение которого данные должны оставаться стабильными после тактового фронта | Поврежденные данные, инверсия битов |

| Смещение тактового сигнала | Разница во времени прихода тактового сигнала к разным чипам | Снижение временного запаса, нестабильность |

| Цикл работы | Отношение времени высокого уровня к общему периоду | Неравномерная производительность, увеличение джиттера |

В DDR4 и DDR5 шина команд и адресов часто работает с более низкой частотой, чем шина данных. Диаграммы временных интервалов должны учитывать сигналы стробирования синхронизации по источнику (DQS), сопровождающие данные, чтобы указать допустимые временные окна.

2. Интерфейсы дисплеев (MIPI DSI)

Мобильные устройства используют последовательный интерфейс дисплея MIPI (DSI) для подключения процессора к экрану. Этот интерфейс использует высокоскоростные дифференциальные линии.

- Режим низкого энергопотребления для команд:Режим низкого энергопотребления для передачи команд, основанный на строгом соблюдении временных интервалов для последовательности пробуждения.

- Режим высокоскоростной передачи данных:Высокоскоростная передача данных, при которой восстановление тактового сигнала производится непосредственно из потока данных.

- Время переключения: Время, необходимое для переключения с режима передачи на режим приема на одной и той же линии.

Несоответствие в этих временных диаграммах приводит к появлению артефактов на экране, мерцанию или полной потере видеовыхода.

📡 Телекоммуникации: задержка и пропускная способность

В телекоммуникациях временная синхронизация эквивалентна задержке. Время доставки пакетов и синхронизация в распределённых сетях критически важны для таких услуг, как 5G и высокочастотная торговля.

1. Сигнализация PCIe

Стандарт Peripheral Component Interconnect Express (PCIe) широко используется для подключения высокоскоростных компонентов. Он использует последовательные каналы с встроенными тактовыми сигналами или тактовыми сигналами, синхронизированными с источником.

- Равномерение:Целостность сигнала ухудшается с расстоянием. Временные диаграммы показывают, как фильтры равномерения компенсируют потери.

- Обучение соединению: Последовательность временных состояний для установления скорости соединения и ширины канала.

- Управление потоком: Временные окна для управления потоком на основе кредитов предотвращают переполнение буферов.

2. Физические уровни Ethernet

Стандартный Ethernet полагается на общий тактовый сигнал или восстановление тактового сигнала. Ethernet на скорости 1 Гбит/с и выше используют кодирование 8b/10b для обеспечения достаточного количества переходов для восстановления тактового сигнала.

- Периоды простоя: Определённые временные интервалы, в течение которых данные не передаются для поддержания синхронизации.

- Разделитель начала кадра: Определённая последовательность битов, обозначающая начало пакета, требующая точного времени обнаружения.

- Интервал между пакетами: Обязательная задержка между пакетами для обеспечения сброса аппаратного обеспечения.

⚠️ Распространённые нарушения временных параметров и решения

Даже при тщательном проектировании нарушаются временные параметры. Для выявления корневой причины необходимо проанализировать временную диаграмму, чтобы определить, где сигналы отклоняются от ожиданий.

1. Нарушения времени установки

Происходит, когда данные приходят слишком поздно, чтобы быть захваченными фронтом тактового сигнала.

- Причины:Чрезмерная глубина логики, большие задержки в проводах или дисбаланс тактового сигнала.

- Решения:

- Вставлять регистры конвейера для разбиения длинных путей.

- Оптимизировать синтез логики для уменьшения количества вентилей.

- Настроить частоту тактового сигнала, чтобы обеспечить больше времени.

2. Нарушения времени удержания

Происходит, когда данные изменяются слишком быстро после фронта тактового сигнала, перезаписывая захваченное значение.

- Причины:Короткие задержки в пути, джиттер тактового сигнала, когда сигнал захвата приходит слишком поздно.

- Решения:

- Вставьте буферы задержки в путь данных.

- Используйте методы перестройки временных интервалов для выравнивания путей.

- Обеспечьте минимальный джиттер в сети распределения тактового сигнала.

3. Джиттер и джиттер тактового сигнала

Джиттер — это разница во времени прихода тактового сигнала на различные регистры. Джиттер — это кратковременное изменение фронта тактового сигнала.

- Влияние:Снижает эффективный временной запас, доступный для данных.

- Решения:

- Используйте генераторы тактовых сигналов с низким джиттером.

- Проектируйте сбалансированные деревья тактовых сигналов с равной длиной трасс.

- Реализуйте фазовые автоподстройки частоты (ФАПЧ), чтобы очистить тактовые сигналы.

✅ Лучшие практики реализации

Достижение надежного временного режима требует системного подхода на протяжении всего жизненного цикла проектирования. Документирование и проверка так же важны, как и сама схема.

1. Определяйте временные ограничения на ранних этапах

Не ждите этапа реализации, чтобы определить временные требования. Документируйте частоты тактовых сигналов, задержки входов и выходов в спецификации проекта. Это гарантирует, что все заинтересованные стороны понимают границы системы.

2. Используйте статический анализ временных характеристик

Инструменты статического анализа временных характеристик (STA) рассчитывают пути с максимальной задержкой без моделирования всех комбинаций входов. Этот метод эффективен и охватывает все возможные состояния, гарантируя, что не будет пропущено ни одного нарушения временных характеристик.

3. Проверяйте с помощью моделирования

Хотя STA является мощным инструментом, динамическое моделирование предоставляет представление о поведении сигналов в конкретных условиях. Используйте моделирование для проверки критических путей, особенно тех, которые включают асинхронную логику или сложные конечные автоматы.

4. Рассмотрение физического проектирования

Физическая компоновка чипа или платы напрямую влияет на временные характеристики.

- Длина проводника:Более длинные проводники вводят большую емкость и сопротивление, увеличивая задержку.

- Кросс-тракинг:Соседние сигналы могут вызывать шум, приводя к ложным переходам.

- Шум источника питания:Падения напряжения могут замедлить скорость переключения вентилей.

🛠️ Устранение неисправностей в реальных сценариях

Когда система не может соответствовать временным требованиям, необходим структурированный процесс отладки. Ниже приведены шаги, описывающие логический подход к устранению временных проблем.

- Шаг 1: Определите путь.Найдите конкретный путь от регистра к регистру, вызывающий сбой. Обратите внимание на отчет по времени с наиболее отрицательным временем задержки.

- Шаг 2: Проанализируйте формы сигналов.Используйте просмотрщик диаграмм времени для проверки фактических переходов сигнала. Сравните их с ожидаемыми значениями.

- Шаг 3: Проверьте тактовый сигнал.Проверьте качество тактового сигнала. Обратите внимание на джиттер, искажение коэффициента заполнения или помехи.

- Шаг 4: Проверьте ограничения.Убедитесь, что ограничения в файле проекта соответствуют физической реальности аппаратного обеспечения.

- Шаг 5: Повторите.Внесите изменения в логику или компоновку, а затем повторно выполните анализ временных параметров.

📊 Сводка по временным параметрам

Для удобства быстрого доступа приведена сводка по ключевым временным параметрам, используемым в различных отраслях.

| Параметр | Символ | Типичная единица измерения | Описание |

|---|---|---|---|

| Период | Tc | нс | Время между последовательными тактовыми фронтами |

| Частота | Fc | Гц | Обратная величина периода |

| Время установки | тсу | нс | Требуется стабильность данных до фронта тактового сигнала |

| Время удержания | тн | нс | Требуется стабильность данных после фронта тактового сигнала |

| Задержка распространения | тпз | нс | Время прохождения сигнала через логику |

| Смещение | Δт | пс | Разница во времени прихода тактового сигнала |

🔄 Управление асинхронными дизайнами

Не все системы работают на одном тактовом сигнале. Асинхронные дизайны включают передачу данных между различными тактовыми доменами. Это создает риск метастабильности, при которой триггер переходит в неопределенное состояние.

- Цепочки синхронизации: Используйте многоступенчатый синхронизатор (обычно два триггера), чтобы дать сигналу успокоиться перед использованием.

- Протоколы рукопожатия: Реализуйте механизмы запроса-подтверждения, чтобы убедиться, что приемник готов перед отправкой данных.

- Буферы FIFO: Используйте структуры памяти по принципу FIFO для разделения скоростей производителя и потребителя.

Диаграммы временных интервалов для асинхронных дизайнов показывают взаимосвязь между двумя независимыми тактовыми сигналами. Ключевым является обеспечение достаточного времени для стабилизации сигнала до момента выборки приемным тактовым сигналом.

🌟 Заключительные мысли

Диаграммы временных интервалов являются основой верификации цифровых систем. Они служат мостом между абстрактной логикой и физической реальностью. Понимая тонкости времени установки, времени удержания, смещения тактового сигнала и джиттера, инженеры могут проектировать системы, которые являются надежными, эффективными и устойчивыми.

Независимо от того, в системах безопасности автомобилей, потребительских устройствах или инфраструктуре телекоммуникаций — принципы остаются неизменными. Точность во времени ведет к точности в производительности. Постоянный мониторинг и соблюдение лучших практик обеспечивают функциональность проектов на протяжении всего жизненного цикла. По мере развития технологий и увеличения скорости важность детального анализа временных интервалов будет только возрастать.

Для команд, стремящихся улучшить качество своего дизайна, затраты времени на точные временные диаграммы и потоки проверки являются обязательными. Это снижает риск, уменьшает затраты на отладку и обеспечивает соответствие конечного продукта его спецификациям. При наличии правильных инструментов и методологий временные проблемы превращаются в управляемые ограничения, а не в препятствия.