在数字电子和计算机工程的世界中,信号并非孤立存在。它们沿着走线传播,穿过门电路,进入处理器,并受到特定时间约束。为了理解系统的工作原理,工程师必须可视化这些信号随时间的变化。这种可视化是通过时序图实现的。对于初学者而言,这些图表可能看起来像复杂的象形文字,但实际上它们是调试和设计数字逻辑最基础的工具。

本指南将全面解析时序图。我们将探讨信号的结构、决定可靠性的关键参数,以及导致系统故障的常见陷阱。无论你是为考试而学习,还是在设计第一个微控制器电路,理解这些图表都是至关重要的。

🧠 什么是时序图?

时序图是数字信号随时间变化状态的图形化表示。与电路原理图不同,后者显示什么连接到什么,时序图显示何时事情发生的时间。它将电压水平与时间轴对应绘制,使工程师能够看到事件的先后顺序。

这些图表之所以不可或缺,原因有以下几点:

- 调试:它们能揭示信号到达顺序混乱的竞赛条件。

- 验证:它们可确认电路是否满足所需的速度规格。

- 文档:它们可作为不同芯片之间通信方式的参考。

- 设计:它们有助于确定系统所能支持的最大时钟频率。

当你查看时序图时,你实际上是在观察电子在系统中运动的物理行为快照。它捕捉了延迟、传播和同步的真实情况。

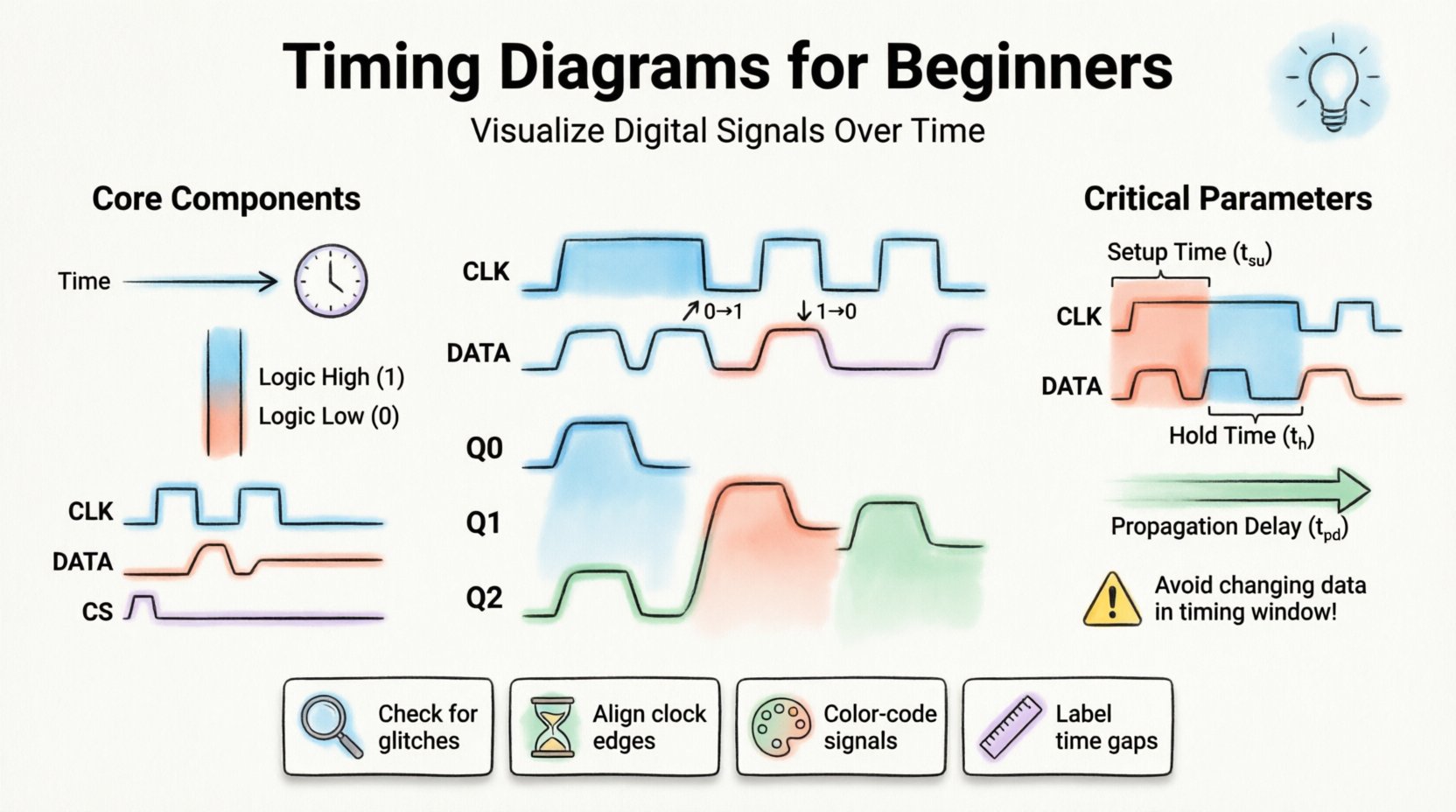

📊 时序图的核心组成部分

在分析复杂波形之前,你必须先理解其基本构成。每个时序图都由几个基本元素组成。

1. 时间轴

水平轴代表时间,从左向右流动。在数字设计中,该轴通常被划分为时钟周期,由垂直网格线标记。量程可从高速处理器的纳秒(ns)到较慢控制逻辑的毫秒(ms)不等。

2. 电压电平轴

垂直轴代表信号的逻辑状态。在标准逻辑家族中,这通常是二进制的:

- 逻辑高电平(1):通常表示为VCC或5V。

- 逻辑低电平(0): 通常表示为地或0V。

- 高阻态(高阻抗): 一种引脚实际上被断开的状态,常见于总线系统中。

3. 信号线

每一根水平线代表一根特定的导线或信号名称。这些线条都有清晰的标签(例如,CLK、DATA_IN、CS),以识别正在被监测的电路部分。

🔄 读取信号跳变

信号线的上下移动就是数据所在的位置。理解这些移动的方向至关重要。

⬆️ 上升沿

当信号从低电平跳变到高电平时,就会出现上升沿。在二进制逻辑中,这通常是许多操作的触发点。它表示从0到1的变化。

⬇️ 下降沿

当信号从高电平跳变到低电平时,就会出现下降沿。这表示从1到0的变化。

⚡ 边沿触发

许多数字元件,如触发器,只对这些边沿做出响应,而不是对稳定状态。触发器可能仅在时钟信号的上升沿时捕获数据。如果你错过了这个边沿,数据就会丢失。

| 跳变 | 方向 | 二进制变化 | 常见触发类型 |

|---|---|---|---|

| 上升沿 | 低 ➔ 高 | 0 ➔ 1 | 正边沿触发 |

| 下降沿 | 高 ➔ 低 | 1 ➔ 0 | 负边沿触发 |

| 高电平 | 稳定高电平 | 稳定1 | 电平敏感 |

| 低电平 | 稳定低电平 | 稳定0 | 电平敏感 |

⏳ 关键时序参数

时序图不仅仅是图片;它们包含测量数据。信号变化之间的间隔决定了可靠性。三个特定参数主导着数字时序分析。

1. 传播延迟(tpd)

信号不会瞬间传输。当输入发生变化时,输出需要经过一定时间才能反映这一变化。这就是传播延迟。它是由材料的物理电阻和电容引起的。

- 定义: 输入变化与输出变化之间的时间差。

- 影响: 在逻辑门链中,延迟会累积。如果延迟过长,信号可能在下一个时钟周期开始后才到达,从而导致错误。

2. 建立时间(tsu)

建立时间是指数据信号必须保持稳定的时间要求在时钟边沿到来之前。如果数据在时钟边沿附近发生改变,接收电路将无法正确捕获它。

- 规则:数据必须在时钟触发前保持有效一段时间。

- 视觉上: 在图中,这是数据线稳定与时钟边沿之间的间隔。

3. 保持时间(th)

保持时间是指数据信号必须保持稳定的时间要求在 当时钟边沿到来时,如果数据在时钟边沿之后立即发生变化,电路可能无法锁存正确的值。

- 规则: 数据在时钟触发后必须保持不变一段时间。

- 视觉上: 在图中,这是时钟边沿与下一次数据跳变之间的间隔。

⚠️ 时序窗口

建立时间和保持时间的组合形成一个有效的数据捕获窗口。如果您的时序图显示数据在此窗口内发生变化,系统就有失败的风险。

⚡ 同步系统与异步系统

时序图的差异显著,取决于系统的架构。

同步系统

在同步设计中,所有操作都由全局时钟信号协调。每次状态变化都发生在该时钟的边沿上。这些系统的时序图看起来非常规律。

- 特点: 可预测,设计更简单,受限于时钟速度。

- 图形外观: 垂直网格线与所有信号变化完全对齐。

异步系统

在异步设计中,没有全局时钟。信号在输入变化时随时改变。这提供了更高的速度潜力,但使时序分析变得困难得多。

- 特点: 对输入响应更快,危险分析更复杂。

- 图形外观: 信号跳变发生在不规则的间隔中。您必须精确测量事件之间的时差。

📝 如何绘制时序图

绘制时序图是一个系统化的过程。按照以下步骤来记录电路或验证设计。

- 识别信号: 列出所有输入、输出和内部控制线。清晰地标记它们。

- 建立时间基准: 确定时间尺度。对于逻辑电路,时钟周期通常是标准单位。

- 绘制时钟: 始终首先绘制时钟信号。它是所有其他事件的参考。

- 映射输入信号: 根据逻辑运算或测试序列绘制输入波形。

- 计算延迟: 根据所涉及门电路的传播延迟,将输出信号向右移动。

- 检查约束条件: 确保每个触发器的建立时间和保持时间都满足要求。

- 检查转换: 确保没有毛刺。毛刺是一种短暂的、意外的脉冲,可能导致逻辑错误触发。

🔄 现实世界示例:一个简单的计数器

为了直观理解这些概念如何协同工作,考虑一个简单的3位二进制计数器。每当时钟信号脉冲时,该电路的值就增加一次。

想象三条输出线:Q0、Q1 和 Q2。Q0 在每个时钟周期都翻转。Q1 每当 Q0 完成一个完整周期时翻转一次。Q2 每当 Q1 完成一个完整周期时翻转一次。

逐步分析

- 时钟 (CLK): 一个占空比为50%的方波。

- Q0(最低位): 在时钟的每个上升沿改变状态。频率为时钟的一半。

- Q1: 在 Q0 的每个上升沿改变状态。频率为 Q0 的一半。

- Q2(最高位): 在 Q1 的每个上升沿改变状态。频率为 Q1 的一半。

绘制时,你会注意到一种涟漪效应。Q0 首先发生变化。Q1 等待 Q0 稳定后才改变。Q2 等待 Q1。这种延迟的累积正是涟漪计数器的本质。

| 时钟周期 | Q2 | Q1 | Q0 | 十进制值 |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ 避免常见陷阱

即使是经验丰富的工程师在阅读时序图时也可能出错。请注意这些常见错误。

- 忽略毛刺: 如果时间尺度太大,短暂的脉冲可能无法显示,但它可能会触发锁存器。务必检查窄脉冲。

- 误解占空比: 假设时钟是50%占空比,但实际上存在偏移。这会影响时序窗口。

- 忽略高阻态: 在总线系统中,信号线处于浮空状态。时序图必须标明信号线是被驱动还是处于浮空状态。

- 混淆建立时间和保持时间: 建立时间在边沿之前;保持时间在边沿之后。混淆二者会导致电路设计错误。

- 忽略接地参考: 所有电压电平都必须相对于同一个地线进行测量。如果地线不同,逻辑电平将无效。

🛠 文档编写的最佳实践

在为文档编写或调试创建时序图时,请遵循以下指南以确保清晰明了。

- 使用一致的缩放比例: 确保时间轴是线性的。除非明确标注,否则不要压缩某一部分而拉伸另一部分。

- 对齐关键边沿: 确保时钟边沿与数据采样点完全对齐。

- 标注间隙: 如果存在延迟,请用具体的时间值进行标注(例如,tpd = 5ns)。

- 颜色编码: 为不同类型的信号使用不同的颜色(例如,蓝色表示时钟,红色表示数据,绿色表示控制信号)。

- 标记有效状态: 明确指出信号是高电平有效还是低电平有效(例如,使用横线表示,如 /CS)。

🧩 亚稳态与时序风险

高级时序图通常会揭示一种称为亚稳态的现象。当信号恰好在触发器的建立/保持窗口内发生变化时就会发生这种情况。输出不会立即稳定到0或1,而是在中间电压电平上徘徊。

尽管罕见,亚稳态仍可能导致系统崩溃。时序图通过展示异步输入与同步时钟之间的关系来帮助预测这一现象。如果外部信号在时钟边沿附近发生改变,图中将显示数据在错误的时间点跨越阈值。

🔍 分析实际数据

当你查看逻辑分析仪生成的时序图时,信号线很少是完美的方波。实际信号具有:

- 上升时间: 从低电平到高电平所需的时间。通常不会瞬间完成。

- 下降时间: 从高电平到低电平所需的时间。

- 过冲/下冲: 超过电源轨的电压尖峰。

- 抖动: 信号边沿时间上的变化。

理解这些不完美之处对于高速设计至关重要。理想的方波只是理论上的概念;实际信号是代表数字逻辑的模拟波形。

📚 主要收获概要

时序图是数字时序的语言。它们将抽象的逻辑转化为物理现实。掌握它们后,您将具备以下能力:

- 可视化数据在系统中的流动。

- 识别信号可能发生冲突的位置。

- 确保数据被可靠捕获。

- 计算电路的最大工作速度。

从简单的逻辑门开始练习。绘制输入信号,计算延迟,并绘制输出。随着进步,逐步转向复杂的总线和时钟域。只要保持耐心并持续练习,阅读这些图表就会变得自然而然。

🚀 继续前进

继续探索信号完整性和时钟分配网络的细微之处。随着系统速度的提升,时序余量会变得更小。准确阅读时序图的能力,将始终是任何从事数字硬件工程的工程师的核心技能。