Compreender o fluxo de sinais ao longo do tempo é fundamental para a eletrônica digital. Para engenheiros de graduação, dominar a interpretação de diagramas de tempo não é apenas um exercício acadêmico; é uma habilidade crítica para projetar sistemas confiáveis. Essas representações visuais mapeiam o comportamento dos sinais ao longo de um eixo do tempo, revelando relações entre ciclos de clock, validade de dados e sinais de controle. Sem um domínio sólido dessas técnicas, até circuitos simples podem falhar em condições do mundo real.

Este guia aborda os princípios fundamentais necessários para ler, criar e analisar diagramas de tempo de forma eficaz. Exploraremos a mecânica do design síncrono e assíncrono, a importância dos tempos de setup e hold, e como evitar armadilhas comuns que levam à falha de circuitos. Ao final deste artigo, você terá uma base sólida para enfrentar problemas complexos de lógica digital.

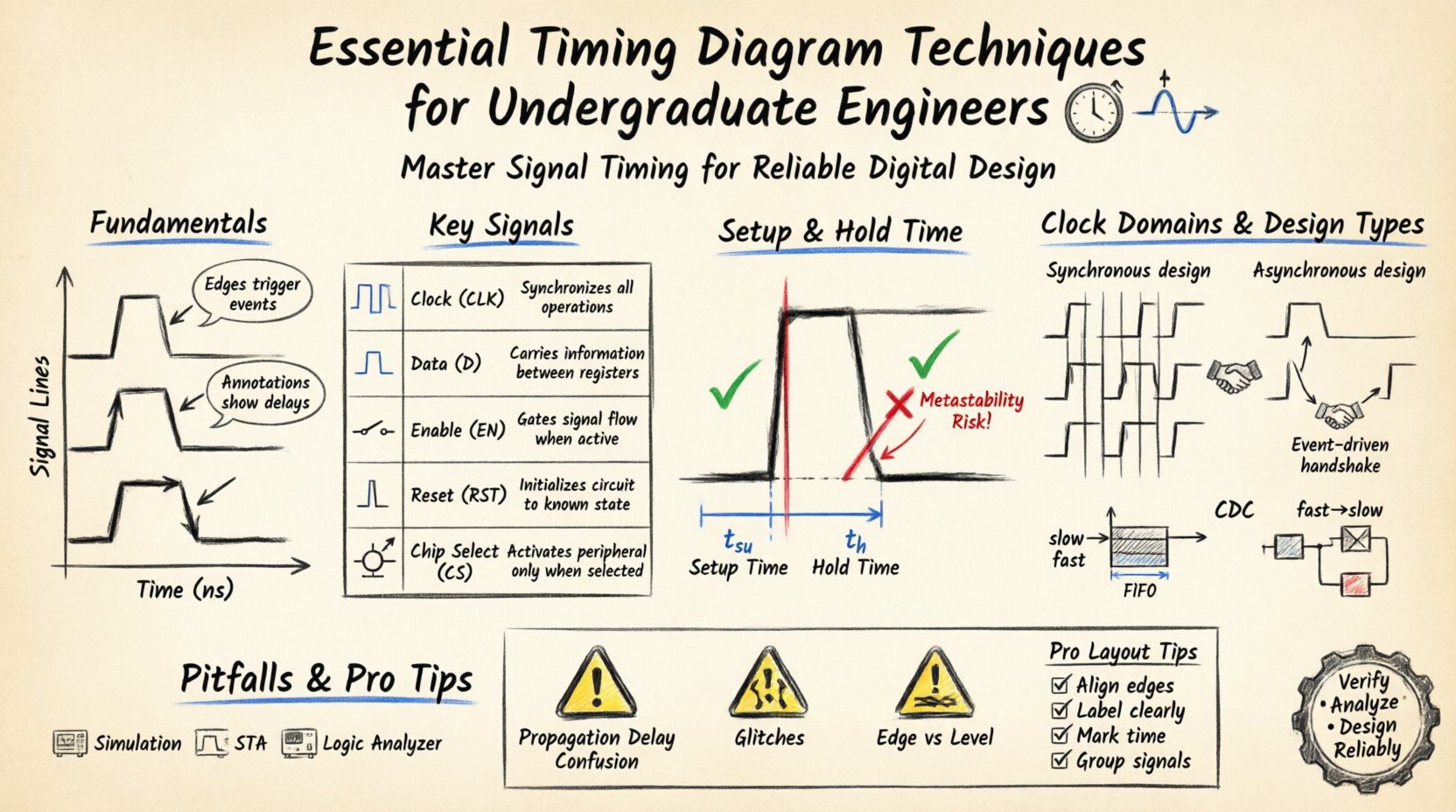

1. Fundamentos dos Diagramas de Tempo 📐

Um diagrama de tempo é uma representação gráfica de sinais ao longo do tempo. Permite que engenheiros visualizem o estado de várias linhas em um circuito digital. Diferentemente dos diagramas lógicos que mostram conectividade, os diagramas de tempo mostram comportamento. São essenciais para depuração, verificação de projetos e comunicação das interações de sinais entre módulos de hardware.

Componentes Principais de um Diagrama de Tempo

- Eixo do Tempo (Eixo X): Representa a progressão do tempo. É geralmente marcado em nanossegundos (ns) ou ciclos de clock.

- Linhas de Sinal (Eixo Y): Linhas horizontais que representam fios individuais ou barramentos. Cada linha corresponde a um nome específico de sinal.

- Níveis Lógicos: Os sinais são geralmente binários, representados como Alto (1) ou Baixo (0). Às vezes, estados ‘High-Z’ (Alta Impedância) aparecem em projetos de barramentos.

- Bordas: Transições verticais indicam uma mudança de estado. As bordas ascendentes (Baixo para Alto) e as bordas descendentes (Alto para Baixo) são críticas para disparar eventos.

- Anotações: Rótulos de texto geralmente indicam atrasos, tempos específicos ou condições que afetam o sinal.

Por que o Tempo Importa na Lógica Digital

Sistemas digitais dependem de uma sincronização precisa. Se um sinal chegar muito cedo ou muito tarde em relação a uma borda de clock, o sistema pode interpretar incorretamente os dados. Diagramas de tempo tornam essas restrições visíveis. Eles ajudam a responder perguntas como:

- Os dados estão estáveis antes da borda de clock?

- Quanto tempo um sinal leva para se propagar por uma porta?

- Dois clocks de domínios diferentes se interferem mutuamente?

2. Sinais e Componentes Principais ⚡

Antes de analisar formas de onda complexas, você deve reconhecer os sinais padrão usados na engenharia digital. Esses sinais determinam como os dados se movem e quando são considerados válidos.

Tipos Comuns de Sinais

| Nome do Sinal | Função | Comportamento Típico |

|---|---|---|

| Clock (CLK) | Fonte de sincronização | Pulsando regularmente entre 0 e 1 |

| Dados (D) | Transportador de informações | Muda de estado com base na entrada ou na lógica |

| Habilitar (EN) | Ativa um módulo | Alto para permitir operação, Baixo para desativar |

| Redefinir (RST) | Inicializa o estado | Pulso Ativo Baixo ou Ativo Alto no início |

| Seleção de Chip (CS) | Seleciona um dispositivo | Ativo Baixo para endereçar um componente específico |

Compreender o estado ativo dos sinais de controle é crucial. Alguns sinais são ativos alto, o que significa que funcionam quando a tensão é alta. Outros são ativos baixo, indicados por uma barra sobre o nome (por exemplo, /RESET ou RST_N), o que significa que funcionam quando a tensão é baixa.

3. Análise de Tempo de Setup e Hold 🕒

Uma das partes mais críticas da análise de tempo envolve os tempos de setup e hold. Esses parâmetros definem a janela em que os dados devem permanecer estáveis em relação a uma borda do clock. Violar essas restrições leva à corrupção de dados ou à metastabilidade.

Tempo de Setup (tsu)

O tempo de setup é a duração mínima durante a qual os dados devem permanecer estáveis antesa chegada da borda ativa do clock. Se os dados mudarem muito perto da borda do clock, o flip-flop pode não capturar o valor correto.

- Requisito:Os dados devem permanecer estáveis por tsuantes da borda ascendente.

- Consequência da Violacão: O registrador pode capturar dados incorretos ou entrar em um estado indefinido.

Tempo de Manutenção (th)

O tempo de manutenção é a duração mínima durante a qual os dados devem permanecer estáveisapóso flanco ativo do clock. O flip-flop precisa de um momento para capturar o valor antes que novos dados cheguem potencialmente.

- Requisito:Os dados devem permanecer estáveis por thapós o flanco ascendente.

- Consequência da violação:Semelhante às violações de setup, isso causa erros de dados ou metastabilidade.

Visualizando os tempos de setup e hold

Ao ler um diagrama de tempo, observe o sinal de dados em relação ao flanco do clock. A linha de dados deve ser plana e inalterada durante a janela de setup (antes) e a janela de hold (depois). Se a linha de dados mudar dentro dessas janelas, o projeto provavelmente está com defeito.

4. Cruzamento de Domínio de Clock ⏱️

Em sistemas complexos, diferentes partes do circuito podem operar em velocidades ou frequências de clock diferentes. O movimento de dados entre esses domínios de clock distintos é conhecido como Cruzamento de Domínio de Clock (CDC). Esse processo introduz desafios significativos de tempo.

Tipos de Domínios de Clock

- Mesma Frequência, Mesma Fase:Projeto síncrono. A análise de tempo simples se aplica.

- Mesma Frequência, Fase Diferente:Requer verificações de alinhamento de fase.

- Frequências Diferentes:Requer técnicas de sincronização como trocas de sinais ou buffers FIFO.

Gerenciando CDC em diagramas de tempo

Ao analisar diagramas com múltiplos domínios de clock, certifique-se de distinguir claramente as linhas de clock. Os dados que cruzam de um domínio lento para um domínio rápido podem ser arriscados se não forem gerenciados. Por outro lado, o cruzamento de rápido para lento pode causar perda de dados se o receptor amostrar muito rapidamente.

- Protocolos de troca de sinais:Use sinais valid/ready para confirmar a conclusão da transferência de dados.

- Buffers FIFO:Desacople as taxas de produção e consumo.

- Sincronizadores:Use flip-flops de múltiplos estágios para reduzir o risco de metastabilidade.

5. Projeto Síncrono vs Assíncrono 🔄

A arquitetura do projeto determina como os diagramas de tempo se apresentam. Compreender a diferença ajuda a prever o comportamento dos sinais.

Projeto Síncrono

A maioria da lógica digital é síncrona. Todas as mudanças de estado ocorrem na borda de um sinal de relógio central.

- Previsibilidade:Mais fácil de analisar porque o tempo é controlado.

- Diagramas de Tempo:Padrões regulares, semelhantes a uma grade. As mudanças de dados alinham-se com as bordas do relógio.

- Limitações:O desvio de relógio pode se tornar um problema em projetos grandes.

Projeto Assíncrono

As mudanças de estado ocorrem com base na chegada dos sinais, e não em um relógio global. Isso é comum em protocolos de handshake e tratamento de interrupções.

- Flexibilidade:Pode ser mais rápido para tarefas específicas, pois espera apenas pelos dados.

- Diagramas de Tempo:Irregular. Os sinais dependem de eventos anteriores, e não de intervalos de tempo fixos.

- Riscos:Susceptível a condições de corrida e perigos se não for cuidadosamente projetado.

6. Armadilhas Comuns e Erros ❌

Mesmo engenheiros experientes cometem erros ao interpretar ou criar diagramas de tempo. Estar ciente desses erros comuns pode poupar muito tempo de depuração.

1. Ignorar o Atraso de Propagação

Os sinais não mudam instantaneamente. As portas têm um atraso de propagação. Se você desenhar um diagrama assumindo mudanças imediatas, sua simulação não corresponderá à realidade.

- Correção:Sempre inclua valores de atraso entre as transições lógicas em seus diagramas.

2. Interpretar incorretamente sinais ativos baixos

Um sinal rotulado como/CSé baixo quando ativo. Se você assumir que está alto, sua lógica será invertida.

- Correção:Verifique o datasheet ou o esquemático para os estados ativos. Procure por bolhas nas portas lógicas.

3. Ignorar transições indesejadas

Transições indesejadas são pulsos curtos e não intencionais. Elas podem ocorrer quando os sinais viajam por caminhos diferentes com atrasos variáveis.

- Correção:Use lógica livre de riscos ou adicione estágios de filtragem no projeto.

4. Confundir borda com nível

Algumas circuitos são acionados na borda ascendente, outras na borda descendente, e outras no próprio nível.

- Correção:Verifique a condição de acionamento na especificação do componente.

7. Leitura e criação de diagramas profissionais 📝

Comunicação clara é vital na engenharia. Um diagrama de tempo bem elaborado transmite informações complexas de primeira vista. Aqui estão as melhores práticas para criá-los.

Melhores práticas para layout

- Alinhe as bordas:Garanta que os sinais relacionados mudem em intervalos consistentes.

- Rotule claramente:Use nomes de sinal, e não apenas linhas genéricas.

- Marque o tempo:Indique a duração dos ciclos ou atrasos específicos.

- Agrupe os sinais:Organize sinais relacionados (como linhas de barramento de dados) juntos.

Processo de criação passo a passo

- Identifique os relógios:Desenhe as linhas de relógio primeiro. Elas são a base do tempo.

- Adicione sinais de controle:Coloque as linhas de habilitação, reinicialização e seleção de chip.

- Plote os dados:Adicione linhas de dados com base no fluxo lógico.

- Anote:Adicione observações sobre tempos de setup/hold ou atrasos específicos.

- Revisão: Verifique violações e consistência lógica.

8. Analisando Cenários do Mundo Real 🔍

Vamos considerar um cenário envolvendo uma operação de leitura de memória. Este é um trabalho comum para engenheiros que trabalham com microcontroladores.

Ciclo de Leitura de Memória

Em uma leitura de memória, o processador envia um endereço, ativa um comando de leitura e aguarda os dados.

- Barramento de Endereços: Válido antes da borda do clock.

- Seleção de Chip: Vai para baixo para ativar a memória.

- Comando de Leitura: Vai para baixo para iniciar a transferência.

- Barramento de Dados: Permanece em High-Z até que a memória o ative.

- Temporização: Os dados devem estar estáveis antes que o processador os amostragem.

Considerações sobre Integridade de Sinal

À medida que a frequência aumenta, a integridade do sinal torna-se um fator importante. Reflexões, crosstalk e ruído podem distorcer os sinais. Os diagramas de temporização em projetos de alta velocidade devem levar em conta esses problemas da camada física.

- Taxa de Subida: Quão rápido o sinal muda. Muito rápido causa ruído; muito lento causa erros de temporização.

- Níveis de Tensão: Certifique-se de que os limiares lógicos sejam atendidos em diferentes temperaturas e variações de tensão.

9. Conceitos Avançados de Temporização 🧠

Para aqueles que desejam aprofundar seus conhecimentos, vários conceitos avançados ampliam a análise básica de temporização.

Metastabilidade

A metastabilidade ocorre quando um flip-flop não consegue se estabilizar em um estado 0 ou 1 estável dentro do tempo necessário. Isso geralmente acontece quando os dados mudam muito perto da borda do clock.

- Probabilidade: É um evento probabilístico, não determinístico.

- Mitigação: Use cadeias de sincronização (vários flip-flops em série) para reduzir a probabilidade a quase zero.

Desvio de Relógio

O desvio de relógio é a diferença nos tempos de chegada do sinal de relógio em diferentes partes do circuito. Um desvio positivo (chega mais tarde) pode ajudar o tempo de setup, mas prejudicar o tempo de hold. Um desvio negativo faz o oposto.

- Impacto no Projeto:O desvio deve ser levado em conta nos orçamentos de tempo.

- Medição:Use osciloscópios ou ferramentas de simulação para medir o desvio.

Jitter

O jitter é a desvios da borda do relógio em relação à sua posição ideal. Ele reduz as margens efetivas de setup e hold.

- Tipos:Jitter de período, jitter ciclo a ciclo e jitter aleatório.

- Impacto:Um alto jitter limita a frequência máxima de operação de um sistema.

10. Ferramentas e Metodologias 🛠️

Embora a análise manual seja educacional, a engenharia moderna depende de ferramentas. No entanto, entender a teoria subjacente é o que permite usar essas ferramentas de forma eficaz.

Software de Simulação

Linguagens de Descrição de Hardware (HDL) permitem simulações. Essas ferramentas geram diagramas de tempo automaticamente a partir do código. Você deve entender a saída para verificar a correção do código.

Análise de Tempo Estática (STA)

Ferramentas de STA verificam matematicamente que todas as trajetórias atendem aos requisitos de tempo sem simulação. Elas verificam violações de setup e hold em todas as condições extremas (temperatura, tensão).

Depuração com Analisadores Lógicos

Debuggers de hardware capturam sinais reais de uma placa. Eles exibem diagramas de tempo que correspondem à realidade, ajudando a identificar problemas na camada física que a simulação pode ignorar.

Conclusão 🏁

Diagramas de tempo são a linguagem do comportamento de sinais digitais. Eles pontuam a lacuna entre a lógica abstrata e a realidade física. Para engenheiros de graduação, investir tempo em dominar essas técnicas traz benefícios ao longo de toda a carreira. Seja você projetando um contador simples ou um processador complexo, a capacidade de ler e analisar restrições de tempo é indispensável.

Ao focar nos tempos de setup e hold, entender domínios de relógio e evitar armadilhas comuns, você constrói uma base sólida. Lembre-se sempre de verificar os estados ativos e considerar os atrasos de propagação. À medida que avança, você encontrará cenários mais complexos, mas os princípios fundamentais permanecem os mesmos. Continue praticando a análise de diagramas, e seus projetos se tornarão mais confiáveis e eficientes.

Continue a aprimorar suas habilidades estudando folhas de dados e analisando formas de onda de circuitos do mundo real. O campo da engenharia digital evolui rapidamente, mas os fundamentos da análise de tempo permanecem constantes.