No mundo intricado da engenharia embarcada, o tempo é tudo. Um microcontrolador pode funcionar perfeitamente em simulação, mas falhar catastroficamente em hardware devido a alguns nanossegundos de atraso. É aqui que o diagrama de temporização se torna uma ferramenta indispensável. Essas representações visuais mapeiam o comportamento dos sinais ao longo do tempo, fornecendo uma visão clara de como os componentes interagem dentro de um sistema digital. Seja você depurando uma falha de comunicação ou projetando uma nova interface de periférico, entender como ler e criar diagramas de temporização é fundamental.

Este guia aborda os mecanismos essenciais da temporização de sinais, desde as definições básicas até interações complexas de protocolos. Exploraremos como interpretar formas de onda, construir diagramas precisos a partir de dados de medição e identificar armadilhas comuns que levam à instabilidade do sistema. Ao dominar essas ferramentas visuais, você ganha a capacidade de prever o comportamento do sistema e validar projetos antes mesmo de saírem da bancada.

🔍 Compreendendo os fundamentos da temporização de sinais

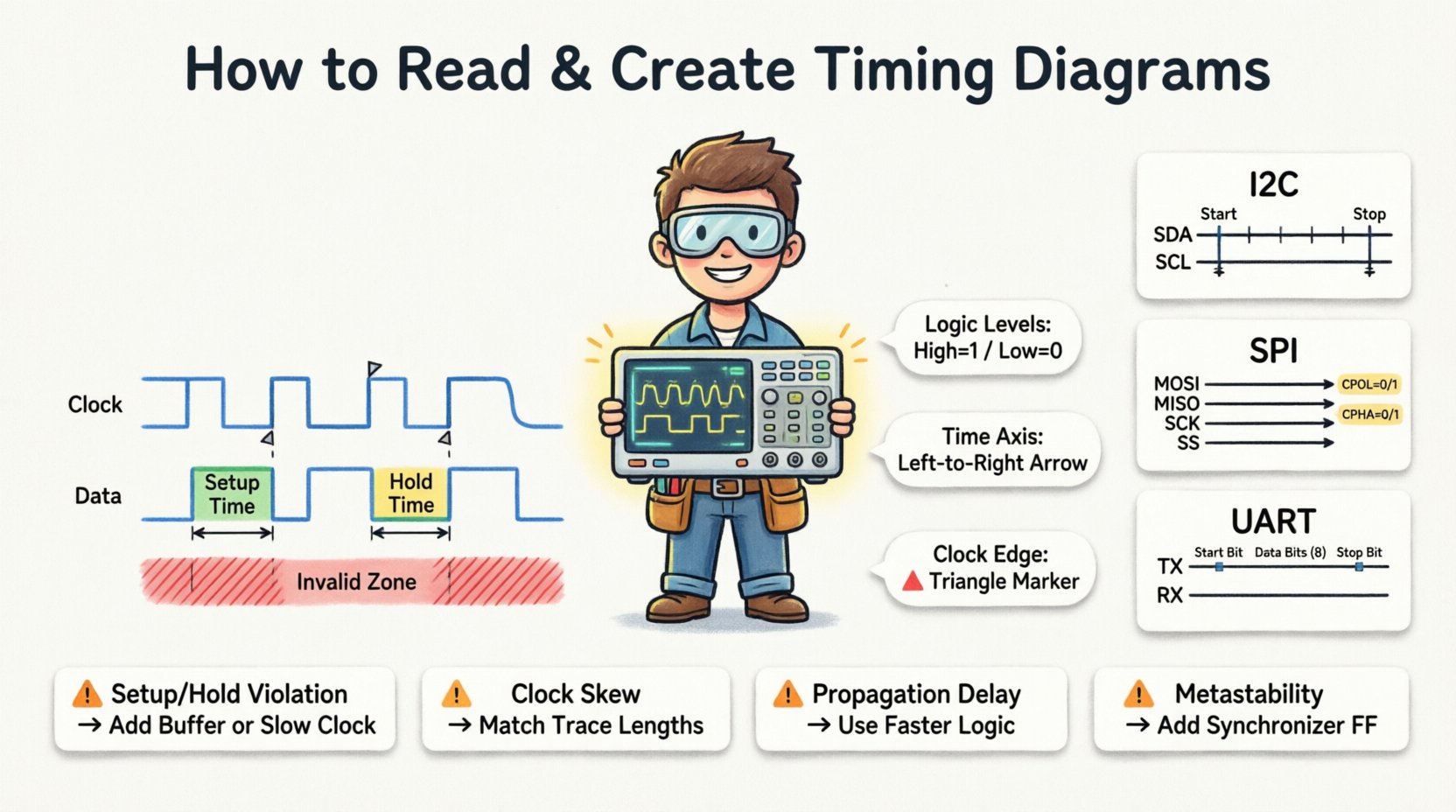

Um diagrama de temporização não é meramente um desenho; é uma representação matemática de estados lógicos em relação a um eixo do tempo. Nos sistemas embarcados, lidamos principalmente com níveis lógicos digitais, que são binários: Alto (1) e Baixo (0). No entanto, as transições entre esses níveis são onde reside a complexidade.

- Níveis Lógicos:A maioria dos sistemas embarcados opera com limites de tensão específicos. Por exemplo, um sistema de 3,3V define Alto como qualquer valor acima de 2,0V e Baixo como qualquer valor abaixo de 0,8V.

- Eixo do Tempo:O tempo flui da esquerda para a direita. O espaçamento horizontal representa a duração de estados específicos ou o atraso entre eventos.

- Traços de Sinal: Cada linha horizontal representa um fio ou rede específico. Várias linhas empilhadas verticalmente permitem a comparação das relações entre sinais.

Ao analisar um sistema, você está procurando por causalidade. O sinal de clock dispara a mudança de dados? O sinal de habilitação precisa estar ativo antes que os dados sejam válidos? Os diagramas de temporização respondem a essas perguntas de forma visual.

🛠️ Componentes Principais de um Diagrama de Temporização

Para interpretar corretamente um diagrama, você deve reconhecer os elementos padrão usados para indicar o comportamento do sinal. Esses componentes definem as regras de interação para o hardware.

| Componente | Descrição | Indicador Visual |

|---|---|---|

| Nome do Sinal | Identifica o fio ou rede específico | Rótulo de texto à esquerda |

| Nível Lógico | Estado Alto (1) ou Baixo (0) | Linha horizontal plana na parte superior ou inferior |

| Aresta de Transição | Mudança de Alto para Baixo ou vice-versa | Linha vertical conectando os níveis |

| Aresta de Clock | Ponto de disparo para lógica síncrona | Linha tracejada ou marcador triangular |

| Zona Inválida | Região onde os dados não podem ser lidos | Área sombreada ou hachurada |

Compreender esses componentes permite que você desmonte interações complexas. Por exemplo, uma área sombreada geralmente indica uma exigência de tempo de preparação ou tempo de retenção em que o dispositivo receptor não consegue capturar os dados de forma confiável.

👁️ Como ler um diagrama de temporização passo a passo

Ler um diagrama de temporização exige uma abordagem sistemática. Você está, essencialmente, traduzindo um padrão visual em uma sequência de eventos. Siga este processo para garantir precisão.

1. Identifique a fonte do clock

A maioria dos sistemas embarcados é síncrona, o que significa que um sinal de clock determina o ritmo das operações. Localize o traçado do clock. Ele geralmente apresenta uma onda quadrada regular e periódica.

- Verifique a frequência. É de 1 MHz ou 100 MHz? Isso determina a velocidade de todo o sistema.

- Identifique o tipo de borda. O dispositivo é acionado pela borda ascendente (Baixo para Alto) ou pela borda descendente (Alto para Baixo)?

2. Mapeie as janelas de validade dos dados

Os dados são válidos apenas durante janelas específicas em relação ao clock. Procure a relação entre a borda do clock e a linha de dados.

- Tempo de preparação: Os dados devem permanecer estáveis por um período determinado antes a borda do clock.

- Tempo de retenção: Os dados devem permanecer estáveis por um período determinado depois a borda do clock.

Se os dados mudarem durante essas janelas, ocorre uma violação de temporização, levando à metastabilidade ou à captura incorreta dos dados.

3. Analise os sinais de controle

Sinais de controle como Chip Select (CS), Enable (EN) ou Reset (RST) determinam quando a comunicação pode ocorrer.

- O Chip Select está ativo baixo ou ativo alto?

- O sinal Enable precisa ser ativado antes que o clock comece a alternar?

- Há eventos assíncronos que sobrepõem a lógica do clock?

4. Verifique os mecanismos de handshake

Muitos protocolos usam handshake para gerenciar o controle de fluxo. Procure sinais de Acknowledge (ACK) ou Ready (RDY).

- O remetente espera por um sinal antes de transmitir o próximo byte?

- Há condições de timeout representadas no diagrama?

📐 Como criar diagramas de temporização precisos

Criar um diagrama de temporização é tão importante quanto lê-lo. Serve como especificação para engenheiros de hardware e como guia de verificação para desenvolvedores de software. Você pode gerá-los a partir de requisitos, ferramentas de medição ou dados de simulação.

Passo 1: Defina os Requisitos do Protocolo

Antes de desenhar, reúna as especificações. Elas geralmente vêm da ficha técnica do componente com o qual você está interagindo.

- Extraia as frequências mínima e máxima do clock.

- Anote os níveis de tensão para lógica Alta e Baixa.

- Registre as restrições de tempo de setup e hold.

Passo 2: Capture os Dados dos Sinais

Use ferramentas de hardware para capturar o comportamento do mundo real. Isso garante que seu diagrama reflita a realidade, e não ideais teóricos.

- Osciloscópios:Melhor para integridade de sinal analógico e níveis de tensão.

- Analizadores Lógicos:Melhor para transições de estado digital e temporização em múltiplas canais.

- Modelos de Simulação:Bom para verificar a lógica antes que o hardware esteja disponível.

Passo 3: Plote as Ondas

Desenhe os sinais em ordem cronológica. Certifique-se de que a escala de tempo seja consistente em todas as canais.

- Use linhas retas para os níveis lógicos.

- Use linhas diagonais para transições, indicando tempos de subida e descida.

- Rotule pontos críticos, como a borda do clock e a mudança de dados.

Passo 4: Anote Restrições Críticas

As anotações fornecem contexto que as imagens sozinhas não conseguem transmitir.

- Marque explicitamente as janelas de tempo de setup e hold.

- Indique a duração de estados específicos do protocolo (por exemplo, Bit de Início, Bit de Término).

- Destaque qualquer latência ou atraso conhecido no caminho do sinal.

🌐 Diagramas de Temporização em Protocolos Embarcados Comuns

Diferentes protocolos de comunicação têm características de temporização distintas. Compreender essas nuances é vital para a integração.

1. Circuito Inter-integrado (I2C)

O I2C é um barramento serial síncrono de dois fios. Ele utiliza SDA (Dados) e SCL (Clock).

- Condição de Início: O SDA transita de Alta para Baixa enquanto o SCL está em Alta.

- Condição de Parada: SDA transita de Baixo para Alto enquanto SCL está Alto.

- Transferência de Dados: Os dados são válidos quando SCL está Alto; as mudanças ocorrem quando SCL está Baixo.

- ACK/NACK: O receptor puxa SDA para Baixo durante o nono pulso de clock para confirmar a recepção.

2. Interface Periférica Serial (SPI)

SPI é um barramento síncrono de quatro fios que oferece velocidades mais altas que o I2C.

- Linhas: MOSI (Saída do Mestre), MISO (Entrada do Mestre), SCK (Clock), SS (Seleção do Escravo).

- CPOL: A Polaridade do Clock determina o estado ocioso (Alto ou Baixo).

- CPHA: A Fase do Clock determina quando os dados são amostrados (primeiro ou segundo borda).

- Seleção do Chip: Deve ser ativado (ativo) antes que o clock comece a alternar.

3. Receptor-Transmissor Assíncrono Universal (UART)

UART é assíncrono, o que significa que não há um sinal de clock compartilhado. O tempo depende das taxas de baud.

- Bit de Início: Puxa a linha para Baixo para sinalizar o início de um quadro.

- Bits de Dados: Transmitido com o bit menos significativo primeiro, geralmente 8 bits.

- Bit de Parada: Puxa a linha para Alto para sinalizar o fim de um quadro.

- Paridade: Bit opcional para verificação de erros.

| Recursos | I2C | SPI | UART |

|---|---|---|---|

| Relógio | Síncrono (Compartilhado) | Síncrono (Compartilhado) | Assíncrono (Sem Relógio) |

| Fios | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| Endereçamento | Sim (Endereço por Byte) | Não (baseado em conexões) | Não |

| Velocidade Máxima | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ Violações Comuns de Temporização e Depuração

Mesmo com um projeto cuidadoso, violações de temporização podem ocorrer. Essas são frequentemente a causa raiz de erros intermitentes que são difíceis de reproduzir.

1. Violações de Tempo de Setup e Hold

Isso acontece quando os dados chegam muito cedo ou muito tarde em relação ao flanco do relógio.

- Sintoma: Corrupção de dados ou erros aleatórios na captura do analisador lógico.

- Solução: Reduza a velocidade do relógio ou otimize os comprimentos das trilhas da placa de circuito impresso.

2. Desvio de Relógio

O desvio de relógio ocorre quando o sinal de relógio chega em componentes diferentes em tempos diferentes.

- Sintoma: Condições de corrida em que um flip-flop captura dados antes que outro esteja pronto.

- Solução: Igualar os comprimentos das trilhas ou usar uma rede dedicada de distribuição de relógio.

3. Atraso de Propagação

Os sinais levam tempo para percorrer fios e portas. Traços longos adicionam atraso significativo.

- Sintoma: Problemas de integridade de sinal ou reflexões em linhas de alta velocidade.

- Solução: Use resistores de terminação e mantenha os traços o mais curtos possível.

4. Metastabilidade

Quando sinais assíncronos cruzam domínios de clock, o flip-flop receptor pode entrar em um estado metastável.

- Sintoma: Travações do sistema ou reinícios aleatórios.

- Solução: Use cadeias de sincronização (dois ou mais flip-flops em série) para resolver o sinal.

📝 Melhores Práticas para Documentação

Criar diagramas de tempo para documentação garante que desenvolvedores futuros possam entender o sistema sem precisar fazer engenharia reversa do hardware.

- Consistência: Use símbolos e estilos de linha padrão em todos os diagramas do projeto.

- Escala: Certifique-se de que o eixo do tempo seja linear e claramente rotulado com unidades (ns, µs, ms).

- Referência: Sempre vincule o diagrama à seção específica da ficha técnica ou ao padrão de protocolo.

- Clareza: Evite bagunça. Se um sinal for estático, mostre-o como uma linha reta em vez de ruído de comutação.

- Versionamento: Atualize os diagramas sempre que o hardware ou firmware mudar significativamente.

🔗 Pensamentos Finais sobre Integridade de Sinal

Diagramas de tempo pontuam a lacuna entre a lógica abstrata e a realidade física. Eles permitem que engenheiros visualizem as restrições invisíveis da eletrônica digital. Ao aprender a lê-los, você pode solucionar problemas complexos de hardware. Ao aprender a criá-los, pode projetar sistemas robustos que funcionem de forma confiável em todas as condições.

O processo envolve paciência e atenção aos detalhes. Cada borda, cada atraso e cada nível de tensão importam. À medida que os sistemas embarcados ficam mais rápidos e complexos, a dependência de diagramas de tempo precisos só aumentará. Trate-os como especificações críticas, e não como documentação opcional.

Comece analisando as fichas técnicas dos componentes que você usa. Procure pelas especificações de tempo. Em seguida, tente desenhar os diagramas com base nesses números. Compare seus desenhos com medições reais obtidas com suas ferramentas. Esse ciclo de previsão e verificação constrói a intuição necessária para o design avançado de sistemas embarcados.

Lembre-se de que um diagrama é uma ferramenta de comunicação. Ele deve transmitir as informações necessárias a outro engenheiro com o mínimo de ambiguidade. Diagramas de tempo claros e precisos reduzem o tempo de desenvolvimento e evitam revisões caras no hardware. Invista o tempo para dominar essa habilidade, e ela trará benefícios ao longo de toda a sua carreira de engenheiro.