В сложной среде цифрового аппаратного проектирования важна ясность. Инженеры и проектировщики полагаются на визуальные представления, чтобы передать, как сигналы ведут себя во времени. Диаграмма временных интервалов является одним из наиболее важных инструментов для этой цели. Она преобразует абстрактную логику в визуальную временную шкалу, раскрывая взаимодействие высоких и низких состояний между различными компонентами. Однако по мере усложнения систем эти диаграммы могут стать чрезмерно перегруженными. В этом руководстве рассматривается модульная стратегия для эффективного анализа и разбора диаграмм временных интервалов, обеспечивая точность и надежность при верификации аппаратного обеспечения.

Понимание потока данных и сигналов управления является ключевым для предотвращения функциональных сбоев. Независимо от того, проектируете ли вы интерфейс микроконтроллера или протокол высокоскоростной связи, способность читать и создавать эти диаграммы разделяет надежный дизайн от хрупкого. Принимая структурированный, модульный подход, команды могут управлять сложностью и снизить риск нарушений временных интервалов.

Понимание основ диаграмм временных интервалов ⏱️

Диаграмма временных интервалов — это графическое представление того, как сигналы изменяют свое состояние во времени. Время откладывается по горизонтальной оси, а состояния сигналов — по вертикальной. Такая визуальная форма позволяет инженерам проверять взаимосвязь между различными сигналами в цифровой схеме. Основная цель — обеспечить, чтобы данные были стабильными и корректными в момент выборки приемным компонентом.

Несколько ключевых элементов составляют основу любой диаграммы временных интервалов:

- Линии сигналов:Горизонтальные линии представляют отдельные провода или шины, передающие конкретные сигналы, такие как тактовый, данные или управление.

- Ось времени:Горизонтальное движение указывает на течение времени, часто обозначаемое в наносекундах или тактовых циклах.

- Уровни логики:Сигналы обычно двоичные, представлены как высокий (1) или низкий (0). Иногда также отображаются неопределенные состояния или состояния высокого импеданса.

- Переходы:Вертикальные линии указывают момент, когда сигнал переключается из одного состояния в другое, например, на восходящем или нисходящем фронтах.

- Примечания:Текстовые метки часто определяют конкретные ограничения, задержки или функциональные блоки внутри диаграммы.

Без четкого понимания этих основ, интерпретация сложных взаимодействий становится трудной. Диаграмма временных интервалов — это не просто рисунок; это договор между передатчиком и приемником. Она определяет правила, по которым данные должны передаваться, чтобы быть корректно обработанными.

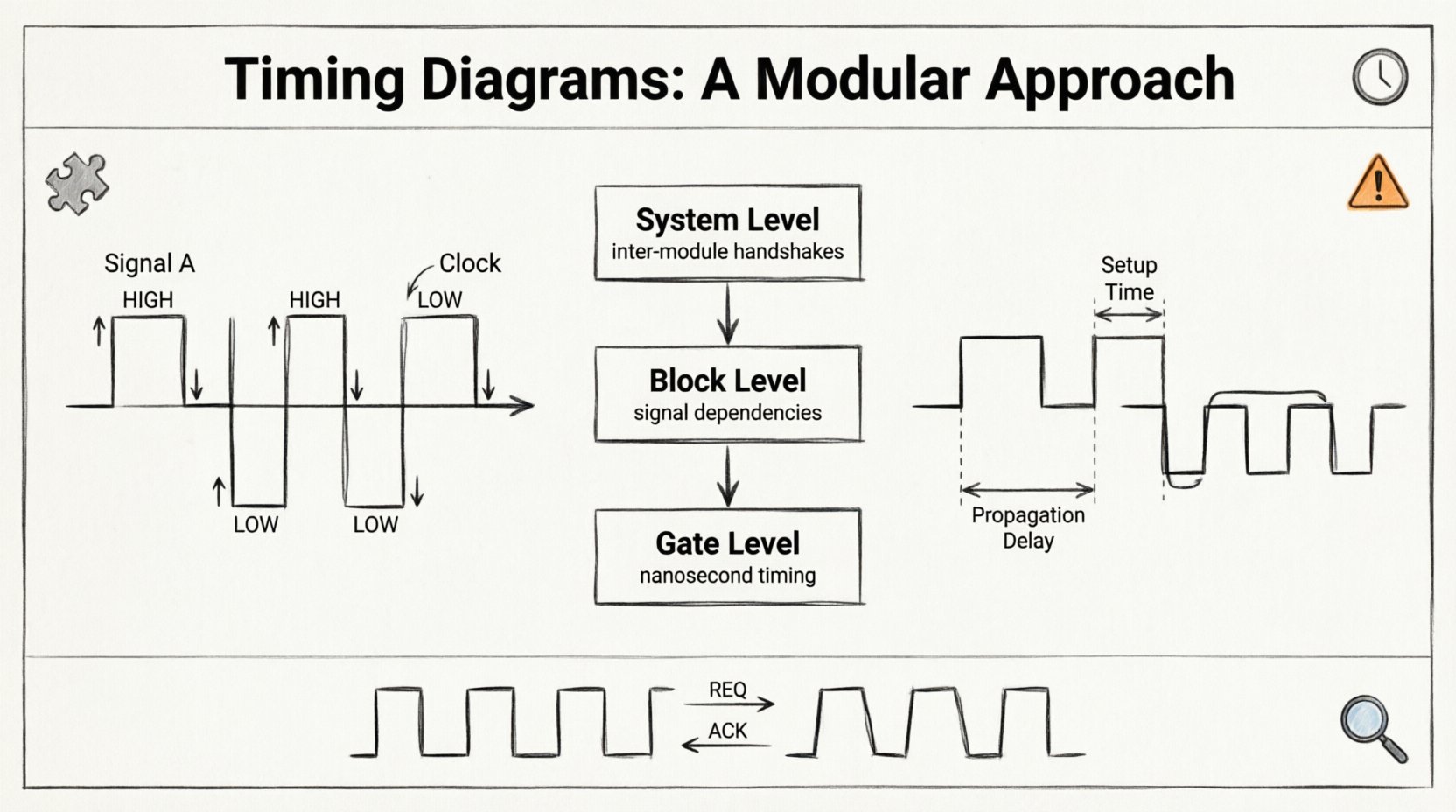

Модульная стратегия для сложных проектов 🧩

Современные цифровые системы редко бывают простыми. Они состоят из нескольких подсистем, каждая из которых имеет свои собственные требования к временным интервалам. Попытка изобразить всю систему на одной диаграмме часто приводит к перегруженности и путанице. Модульный подход разбивает проектирование на управляемые части. Этот метод повышает читаемость и упрощает процесс отладки.

Почему модульность важна

Разбиение системы на модули позволяет проектировщикам сосредоточиться на конкретных интерфейсах, не теряясь в шуме всей архитектуры. Когда возникает нарушение временных интервалов, модульная диаграмма облегчает локализацию источника проблемы. Это снижает когнитивную нагрузку и способствует сотрудничеству между различными инженерными командами, работающими над отдельными блоками.

Преимущества этого подхода включают:

- Изоляция проблем:Проблемы можно выявить в конкретном блоке, а не во всей системе.

- Повторное использование:Стандартизированные временные паттерны для распространенных модулей можно использовать в разных проектах.

- Масштабируемость:Новые функции можно добавлять как новые модули, не перерисовывая всю диаграмму.

- Эффективность команды:Разные команды могут одновременно работать над своими диаграммами временных интервалов.

Определение границ модуля

Для эффективной реализации этой стратегии необходимо установить четкие границы. У каждого модуля должны быть определенные входы и выходы. Диаграмма временных зависимостей для одного модуля должна фокусироваться на сигналах, пересекающих эти границы. Внутренние детали можно абстрагировать, если они не влияют непосредственно на временные характеристики интерфейса.

| Уровень модуля | Область фокусировки | Уровень детализации |

|---|---|---|

| Уровень системы | Взаимодействие между модулями | Высокоуровневые согласования |

| Уровень блока | Внутренние пути передачи данных | Конкретные зависимости сигналов |

| Уровень вентиля | Задержки распространения | Точное временнóе значение в наносекундах |

Организуя диаграммы в соответствии с этими уровнями, инженеры могут поддерживать четкую иерархию информации. Такая структура обеспечивает наличие соответствующего уровня детализации на каждом этапе проектирования.

Декодирование состояний и переходов сигналов 📊

Как только модульная структура будет установлена, следующим шагом является анализ конкретных сигналов. Не все сигналы ведут себя одинаково. Некоторые являются непрерывными, а другие — срабатыванием по фронту. Понимание природы каждого сигнала имеет решающее значение для точного построения диаграмм.

К распространенным категориям сигналов относятся:

- Сигналы тактирования: Сердцебиение системы. Эти сигналы периодические и вызывают смену состояний. Обычно у них строгие требования к частоте и коэффициенту заполнения.

- Сигналы данных: Непосредственно передаваемая информация. Они должны быть стабильными в определённых временных окнах относительно тактового сигнала.

- Управляющие сигналы: Сигналы, которые включают или отключают функциональность, например, Chip Select или Enable.

- Сигналы сброса: Сигналы инициализации, которые вынуждают систему перейти в известное состояние.

Переходы на этих линиях имеют критическое значение. Растущий фронт часто запускает действие, а спадающий — может завершить его. В асинхронных системах взаимосвязь между этими фронтами менее предсказуема, что требует более детального анализа.

Визуализация задержки распространения

Никакой сигнал не изменяется мгновенно. Физические ограничения вызывают задержку распространения. Когда сигнал покидает компонент, проходит время, пока он не пройдёт по проводу и не достигнет следующего компонента. Диаграммы временных зависимостей должны учитывать эту задержку. Если диаграмма показывает изменение сигнала в момент времени T, то приёмная сторона может не увидеть его до момента T + Δt.

Пренебрежение задержкой распространения может привести к серьёзным ошибкам при моделировании и реализации. Инженеры должны моделировать эти задержки, чтобы обеспечить соблюдение времён установки и удержания на всём протяжении пути.

Объяснение критических временных ограничений ⚠️

Наиболее распространенной причиной сбоя в цифровом дизайне является нарушение временных ограничений. Эти нарушения возникают, когда сигналы не соответствуют требуемым окнам стабильности. Два основных ограничения управляют этим поведением: время установки и время удержания.

Время установки

Время установки — это минимальное время, в течение которого данные должны оставаться стабильными до активного фронта тактового сигнала. Если данные приходят слишком поздно, триггер может не захватить правильное значение. Это ограничение критически важно для определения максимальной рабочей частоты системы. Если период тактового сигнала короче, чем сумма времени распространения и времени установки, система выйдет из строя.

Ключевые аспекты, связанные со временем установки, включают:

- Для определения худшего случая требуется анализ самого длинного пути.

- Вариации процесса, напряжения и температуры влияют на задержку.

- Джиттер тактового сигнала может сокращать доступное окно времени установки.

Время удержания

Время удержания — это минимальное время, в течение которого данные должны оставаться стабильными после активного фронта тактового сигнала. Если данные изменяются слишком быстро, триггер может захватить неправильное значение или перейти в метастабильное состояние. В отличие от времени установки, время удержания не зависит от частоты тактового сигнала. Оно зависит от внутренней задержки компонента и внешнего пути.

Нарушения времени удержания часто сложнее исправить, поскольку их нельзя устранить за счет замедления тактового сигнала. Вместо этого требуется добавление задержки в путь данных или переработка логики.

Сводка временных ограничений

| Ограничение | Определение | Влияние на частоту | Метод устранения |

|---|---|---|---|

| Время установки | Стабильность до фронта тактового сигнала | Ограничивает максимальную частоту | Оптимизировать логический путь |

| Время удержания | Стабильность после фронта тактового сигнала | Независимо от частоты | Добавить задержку буфера |

| Время распространения | Время прохождения через логику | Влияет на оба | Оптимизация схемы |

Распространённые ошибки и нарушения 🚫

Даже при модульном подходе ошибки могут проникнуть в систему. Распознавание распространённых ошибок помогает избежать их на этапе проектирования. При проверке аппаратных средств часто возникают различные типы нарушений.

- Метастабильность: Происходит, когда сигнал изменяется точно в момент фронта тактового сигнала. Выход триггера становится непредсказуемым. Это часто происходит при переходе между тактовыми доменами.

- Метки: Короткие, нежелательные импульсы, вызванные различиями в логических путях. Они могут вызвать ложные изменения состояния.

- Сдвиг тактового сигнала: Когда тактовый сигнал приходит в различные компоненты в разное время. Это уменьшает эффективное временнóе окно.

- Гонки условий: Когда результат зависит от последовательности событий, что непредсказуемо в асинхронных схемах.

Для решения этих проблем требуется тщательный анализ временной диаграммы. Ищите перекрывающиеся окна, где стабильность не гарантирована. Убедитесь, что последовательности сброса выполняются правильно, чтобы избежать неопределённых состояний.

Реализация модульного рабочего процесса 🛠️

Чтобы эффективно применить этот метод, следуйте структурированному рабочему процессу. Это гарантирует, что каждый аспект временных параметров будет учтён без избыточности.

- Определите интерфейсы: Чётко перечислите все входы и выходы для каждого модуля.

- Определите тактовые домены: Определите, к какому тактовому домену относятся те или иные сигналы.

- Создайте карту путей передачи данных: Проделайте путь от источника до назначения.

- Примените ограничения: Установите требования по установке и удержанию для каждого триггера.

- Проверьте переходы: Проверьте выравнивание фронтов и длительность импульсов.

- Проверьте интеграцию: Убедитесь, что диаграммы модулей совпадают при объединении.

Каждый шаг опирается на предыдущий. Пропуск шага может привести к пробелам в покрытии. Например, игнорирование тактовых доменов может привести к сбоям синхронизации, которые сложно отлаживать позже.

Обработка многосекционных тактовых доменов 🌐

По мере роста сложности схемы возникает необходимость в нескольких частотах тактового сигнала. Некоторые части системы работают быстро, другие — медленно. Синхронизация этих доменов является одной из самых сложных задач при анализе временных параметров.

Когда сигналы переходят из одного тактового домена в другой, временная диаграмма должна отражать взаимосвязь между двумя тактовыми сигналами. Если тактовые сигналы асинхронны, требуется особое внимание, чтобы предотвратить метастабильность. Для безопасной передачи используются такие методы, как цепочки синхронизаторов или протоколы рукопожатия.

Ключевые стратегии для многотактовых схем включают:

- Код Грея: Использование кодов Грея для безопасной передачи многоразрядных счётчиков между доменами.

- Буферы FIFO: Использование очередей по принципу «первым пришел — первым обслужен» для разделения тактов чтения и записи.

- Сигналы согласования: Использование пар запрос/подтверждение для обеспечения достоверности данных.

Диаграммы временных интервалов для этих сценариев должны явно показывать фронты тактовых сигналов обоих доменов. Это позволяет инженерам убедиться, что данные остаются стабильными достаточно долго, чтобы приемный тактовый сигнал мог их захватить.

Отладка с использованием визуальных данных 🔍

Когда проект не работает, первое, что нужно проверить — это диаграммы временных интервалов. Отладка требует терпения и системного подхода. Начните с изоляции неисправного модуля. Сравните ожидаемую диаграмму с фактической формой сигнала.

Ищите расхождения в:

- Время сигнала относительно тактового сигнала.

- Ширина импульса управляющих сигналов.

- Переходы состояний во время сброса.

- Всплески на линиях данных.

Инструменты часто предоставляют функции масштабирования для анализа деталей на уровне наносекунд. Используйте эти функции, чтобы проверить точный момент возникновения нарушения. Сопоставьте визуальные данные с логикой, чтобы понять коренную причину.

Заключительные мысли о целостности проектирования 💡

Диаграммы временных интервалов — это больше, чем просто технические чертежи; они являются чертежом надежных цифровых систем. Принимая модульный подход, инженеры могут управлять сложностью и сохранять ясность. Такой метод способствует масштабируемости и снижает вероятность дорогостоящих ошибок.

Успех в проектировании аппаратных средств зависит от внимания к деталям. Каждая наносекунда имеет значение. Каждый переход важен. Применяя эти принципы строго, команды могут создавать системы, которые надежно работают в реальных условиях. Модульный анализ временных интервалов гарантирует, что ни одна деталь не будет упущена, что приводит к прочным и эффективным аппаратным решениям.

Постоянное совершенствование этих навыков необходимо по мере развития технологий. Новые стандарты и более высокие скорости требуют обновленных методов анализа. Оставайтесь в курсе появляющихся лучших практик, чтобы сохранить конкурентное преимущество в области цифрового проектирования.