В цифровой электронике и компьютерной инженерии понимание временных отношений между сигналами является фундаментальным для надежности системы. Диаграмма временных интервалов служит основным визуальным языком для описания этих отношений. Она отображает состояния сигналов по оси времени, позволяя инженерам визуализировать поток данных, синхронизацию тактового сигнала и возможные опасности в цепи. В этом руководстве рассматриваются структурные элементы, рабочие паттерны и критические сценарии, встречающиеся при анализе сигналов.

Независимо от того, проектируете ли вы интегральные схемы или отлаживаете встраиваемые системы, способность интерпретировать и создавать точные временные представления является ключевым навыком. В этом документе представлен технический обзор взаимодействия сигналов, ограничений, которым они должны подчиняться, и распространённых ошибок, возникающих при проверке.

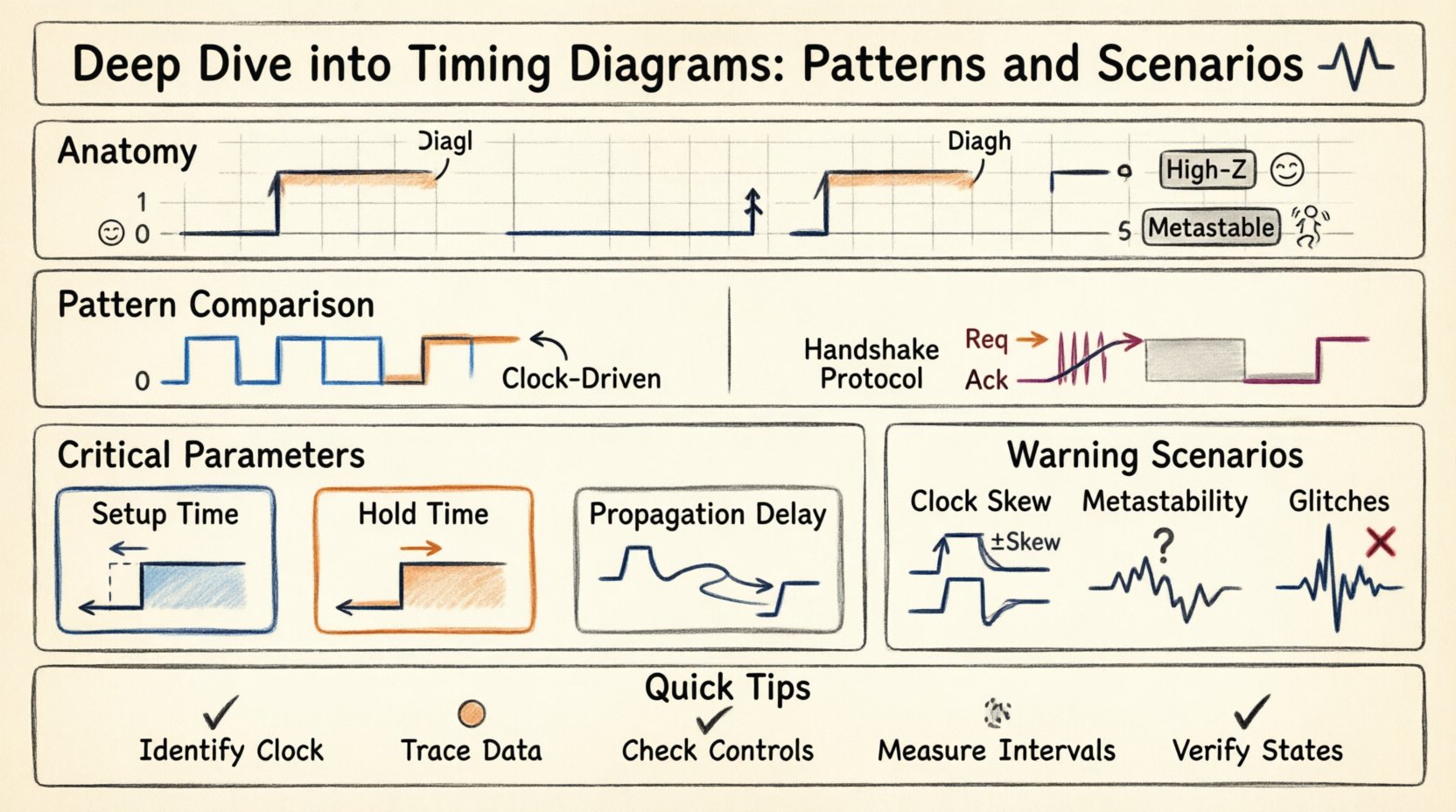

📐 Анатомия диаграммы временных интервалов

Диаграмма временных интервалов — это графическое представление, где горизонтальная ось обозначает время, а вертикальная — уровни сигналов. Каждая горизонтальная линия соответствует определённому сигналу или цепи в проекте. Понимание компонентов — первый шаг к точному анализу.

- Ось времени: Обычно проходит горизонтально слева направо. Может быть линейной или логарифмической, в зависимости от масштаба наблюдаемых событий.

- Линии сигналов: Отдельные следы, представляющие уровни напряжения. Высокое напряжение обычно обозначает логическую 1, а низкое — логический 0.

- Переходы: Вертикальные линии, указывающие на изменение состояния, например, нарастающий фронт (0 на 1) или спадающий фронт (1 на 0).

- Метки: Текстовые аннотации, идентифицирующие конкретные сигналы, выводы или линии управления.

- Маркеры: Вертикальные штриховые линии, часто используемые для обозначения конкретных событий, таких как тактовый импульс или сигнал сброса.

🔢 Уровни и состояния логики

Цифровые сигналы не всегда строго находятся на уровне 0 или 1. В реальных условиях сигналы могут находиться в неопределённых состояниях или в состоянии высокого импеданса. Полная диаграмма должна учитывать эти вариации.

- Логическая высокая (1): Сигнал подаётся на уровень напряжения, признанный логической истиной.

- Логический низкий (0): Сигнал подаётся на уровень напряжения, признанный логической ложью.

- Высокий импеданс (High-Z): Сигнал отключён от источника, фактически «плавающий». Это распространено в трёхсостоятельных буферах.

- Метастабильное: Состояние, при котором сигнал одновременно не высокий и не низкий, часто возникающее при асинхронных переходах.

⚙️ Распространённые временные паттерны

Проектирование следует предсказуемым паттернам для обеспечения целостности данных. Эти паттерны определяют, как данные перемещаются относительно управляющих сигналов. Распознавание этих паттернов помогает в проверке соответствия проекта его спецификациям.

📌 Синхронный обмен данными

Синхронные проекты полагаются на глобальный тактовый сигнал для координации действий. Данные выбираются только в определённые моменты, как правило, на нарастающем или спадающем фронте тактового сигнала.

- Управление по тактовому сигналу: Все изменения состояния происходят по отношению к фронту тактового сигнала.

- Валидность данных:Данные должны быть стабильными до фронта тактового сигнала и оставаться стабильными после него.

- Распространение:Между фронтом тактового сигнала и моментом изменения выходного сигнала существует задержка.

📌 Асинхронное согласование

Асинхронная связь не зависит от общего тактового сигнала. Вместо этого она использует управляющие сигналы для указания момента, когда данные готовы, и момента, когда они были получены.

- Запрос (Req):Отправитель сигнализирует о наличии данных.

- Подтверждение (Ack):Получатель сигнализирует, что данные были приняты.

- Состояния ожидания:Отправитель может приостановить работу до тех пор, пока получатель не будет готов.

| Функция | Синхронный паттерн | Асинхронный паттерн |

|---|---|---|

| Согласование | Глобальный тактовый сигнал | Управляющие сигналы согласования |

| Скорость | Обычно выше | Переменная, зависит от ответа |

| Сложность | Сеть распределения тактового сигнала | Логика протокола |

| Задержка | Предсказуемая | Переменная |

⏱️ Критические параметры временных интервалов

Помимо визуальных линий, конкретные числовые ограничения определяют, будет ли схема работать корректно. Эти параметры критически важны для статического анализа временных интервалов и должны быть проверены на соответствие физическим пределам.

🛑 Время установки

Время установки — это минимальное время, в течение которого сигнал данных должен оставаться стабильным до фронта тактового сигнала. Если данные изменяются слишком близко к фронту тактового сигнала, приемный триггер может не захватить правильное значение.

- Измерение: Измеряется от активного фронта тактового сигнала назад во времени.

- Риск: Нарушение приводит к неверному захвату данных.

- Требование: Задержка в цепи данных должна быть достаточной, чтобы соответствовать окну установки.

🛑 Время удержания

Время удержания — это минимальное время, в течение которого сигнал данных должен оставаться стабильным после фронта тактового сигнала. Это обеспечивает, что защелка получит достаточно времени для фиксации входного значения.

- Измерение: Измеряется от активного фронта тактового сигнала вперед во времени.

- Риск: Нарушение приводит к метастабильности или захвату неверных данных.

- Требование: Задержка в цепи данных должна быть достаточной короткой, чтобы обеспечить окно удержания.

⚡ Время распространения

Это время, необходимое для прохождения сигнала от входа логического элемента до его выхода. Оно зависит от емкости нагрузки и внутреннего сопротивления транзистора.

- tpd (с высокого на низкий): Время перехода от 1 к 0.

- tpd (с низкого на высокий): Время перехода от 0 к 1.

- Сдвиг: Различия во времени задержки между параллельными путями.

🚨 Критические сценарии временных задержек

Некоторые сценарии представляют значительные трудности, требующие тщательного анализа. Эти ситуации часто связаны с взаимодействием между различными тактовыми доменами или физическими ограничениями аппаратного обеспечения.

🔄 Смещение тактового сигнала

Смещение тактового сигнала возникает, когда тактовый сигнал приходит в различные компоненты в разное время. Это может происходить из-за различий в маршрутизации или физического расстояния.

- Положительное смещение: Тактовый сигнал назначения приходит позже, чем тактовый сигнал источника.

- Отрицательное смещение: Тактовый сигнал назначения приходит раньше, чем тактовый сигнал источника.

- Влияние: Может эффективно уменьшить запасы времени установки или увеличить нарушения времени удержания.

🌊 Метастабильность

Метастабильность — это состояние, при котором выход триггера не является ни высоким, ни низким. Она обычно возникает при нарушении времени установки или удержания, особенно при асинхронных переходах.

- Разрешение: Цепь в конечном итоге переходит в устойчивое состояние, но время, затраченное на это, непредсказуемо.

- Исправление: Используйте синхронизаторы (многоступенчатые триггеры), чтобы снизить вероятность сбоя.

- Среднее время между отказами (MTBF): Среднее время между отказами рассчитывается на основе скорости разрешения метастабильности.

📉 Ложные импульсы

Ложные импульсы — это кратковременные всплески сигнала, которые могут быть ошибочно приняты за действительные переходы. Они часто возникают из-за различий во времени распространения по разным путям.

- Причины:Неравные длины путей или условия гонки.

- Воздействие: Могут вызвать нежелательные изменения состояния в последующей логике.

- Снижение риска: Используйте фильтрующую логику или обеспечьте правильное завершение временных параметров.

🔍 Анализ форм сигналов

При анализе диаграммы временных интервалов систематический подход гарантирует, что ни один деталь не будет упущен. Инженеры должны отслеживать поток данных и управляющих сигналов, чтобы выявить расхождения.

🔍 Пошаговый анализ

- Определите тактовый сигнал: Найдите основной тактовый сигнал. Определите, является ли он срабатывающим по фронту или по спаду.

- Отслеживайте пути данных: Следуйте по линиям данных от источника к месту назначения.

- Проверьте управляющие сигналы:Убедитесь, что сигналы разрешения, сброса и очистки правильно активированы.

- Измерьте интервалы:Рассчитайте время между конкретными событиями, чтобы проверить требования к установке и удержанию.

- Проверьте переходы состояний:Убедитесь, что выходное состояние соответствует ожидаемой логической функции.

🔍 Срабатывание по фронту сигнала

Понимание того, как компонент реагирует на фронты сигнала, имеет решающее значение.

- Срабатывание по положительному фронту:Действие происходит при переходе от низкого уровня к высокому.

- Срабатывание по отрицательному фронту:Действие происходит при переходе от высокого уровня к низкому.

- Срабатывание по уровню:Действие происходит до тех пор, пока сигнал остается на определенном уровне.

🛠️ Стандарты документации

Четкая документация обеспечивает понимание проектов другими инженерами. Согласованность в обозначениях и маркировке предотвращает неправильную интерпретацию при отладке или передаче проекта.

📝 Правила маркировки

- Имена сигналов:Используйте единые правила именования (например,

clk,rst_n,data_in). - Полярность:Четко указывайте сигналы с активным низким уровнем, часто с помощью черты или суффикса.

- Единицы измерения:Четко укажите единицы времени (нс, мкс, мс) на оси времени.

- Масштаб: Убедитесь, что временной масштаб соответствует отображаемым событиям.

📝 Визуальная ясность

- Интервалы: По возможности избегайте пересечения линий.

- Контраст: Используйте различные цвета или толщину линий для разных типов сигналов.

- Примечания: Добавьте примечания, поясняющие сложное поведение или конкретные ограничения.

- Сетка: Используйте сетку в качестве фона для облегчения измерения временных интервалов.

🚧 Процесс устранения неполадок

Когда проект не соответствует требованиям по времени, структурированный процесс устранения неполадок помогает выявить коренную причину. Это включает в себя анализ диаграммы с учетом физических ограничений.

🚧 Выявление нарушений

- Проверьте время установки: Данные приходят слишком поздно по отношению к тактовому сигналу?

- Проверьте время удержания: Данные изменяются слишком быстро после тактового сигнала?

- Проверьте частоту тактового сигнала: Период тактового сигнала короче требуемого минимального значения?

🚧 Стратегии смягчения

- Регистры конвейера: Вставьте дополнительные регистры для разрыва длинных комбинаторных путей.

- Гейтинг тактового сигнала: Снижайте активность для уменьшения энергопотребления и потенциального улучшения временных характеристик.

- Вставка буферов: Добавьте буферы для выравнивания задержек по параллельным путям.

- Ограничения по времени: Определите ложные пути, чтобы исключить логику, не влияющую на поток данных.

📈 Лучшие практики проектирования

Принятие лучших практик на этапе проектирования снижает вероятность возникновения проблем со временем на более поздних этапах жизненного цикла разработки. Прогнозирование и планирование более эффективны, чем реактивное устранение неисправностей.

- Стандартизируйте интерфейсы: Используйте известные протоколы передачи данных для упрощения проверки временных параметров.

- Минимизируйте асинхронные пути: Сведите асинхронные взаимодействия к минимуму, чтобы снизить риски метастабильности.

- Документируйте допущения: Четко укажите частоты тактовых сигналов и уровни напряжения в спецификациях проекта.

- Регулярно проводите проверки: Проводите проверки временных параметров на каждом ключевом этапе проекта.

🎯 Обзор ключевых концепций

Диаграммы временных интервалов являются необходимыми инструментами для визуализации временного поведения цифровых систем. Они показывают, как данные и управляющие сигналы взаимодействуют во времени, выявляя критические ограничения, такие как времена установки и удержания. Понимая структуру этих диаграмм, инженеры могут выявлять закономерности, прогнозировать ошибки и обеспечивать надежную работу системы.

Ключевые выводы включают различие между синхронными и асинхронными паттернами, важность управления джиттером тактового сигнала и необходимость соблюдения четких стандартов документирования. Соблюдение этих принципов способствует надежному проектированию и упрощает процесс проверки.

Непрерывный анализ данных осциллограмм гарантирует, что проекты остаются в пределах рабочих параметров. По мере развития технологий и увеличения частоты тактовых сигналов точность анализа временных параметров становится еще более критичной. Овладение этими концепциями позволяет создавать стабильные, высокопроизводительные цифровые архитектуры.