Na eletrônica digital e na engenharia de computadores, compreender a relação temporal entre os sinais é fundamental para a confiabilidade do sistema. Um diagrama de tempo serve como a linguagem visual principal para descrever essas relações. Ele mapeia os estados dos sinais em relação a um eixo do tempo, permitindo que engenheiros visualizem o fluxo de dados, a sincronização do clock e os possíveis riscos dentro de um circuito. Este guia explora os elementos estruturais, os padrões operacionais e os cenários críticos encontrados na análise de ondas.

Seja no projeto de circuitos integrados ou na depuração de sistemas embarcados, a capacidade de interpretar e criar representações de tempo precisas é uma competência essencial. Este documento fornece uma visão técnica sobre como os sinais interagem, as restrições que devem atender e os armadilhas comuns encontradas durante a verificação.

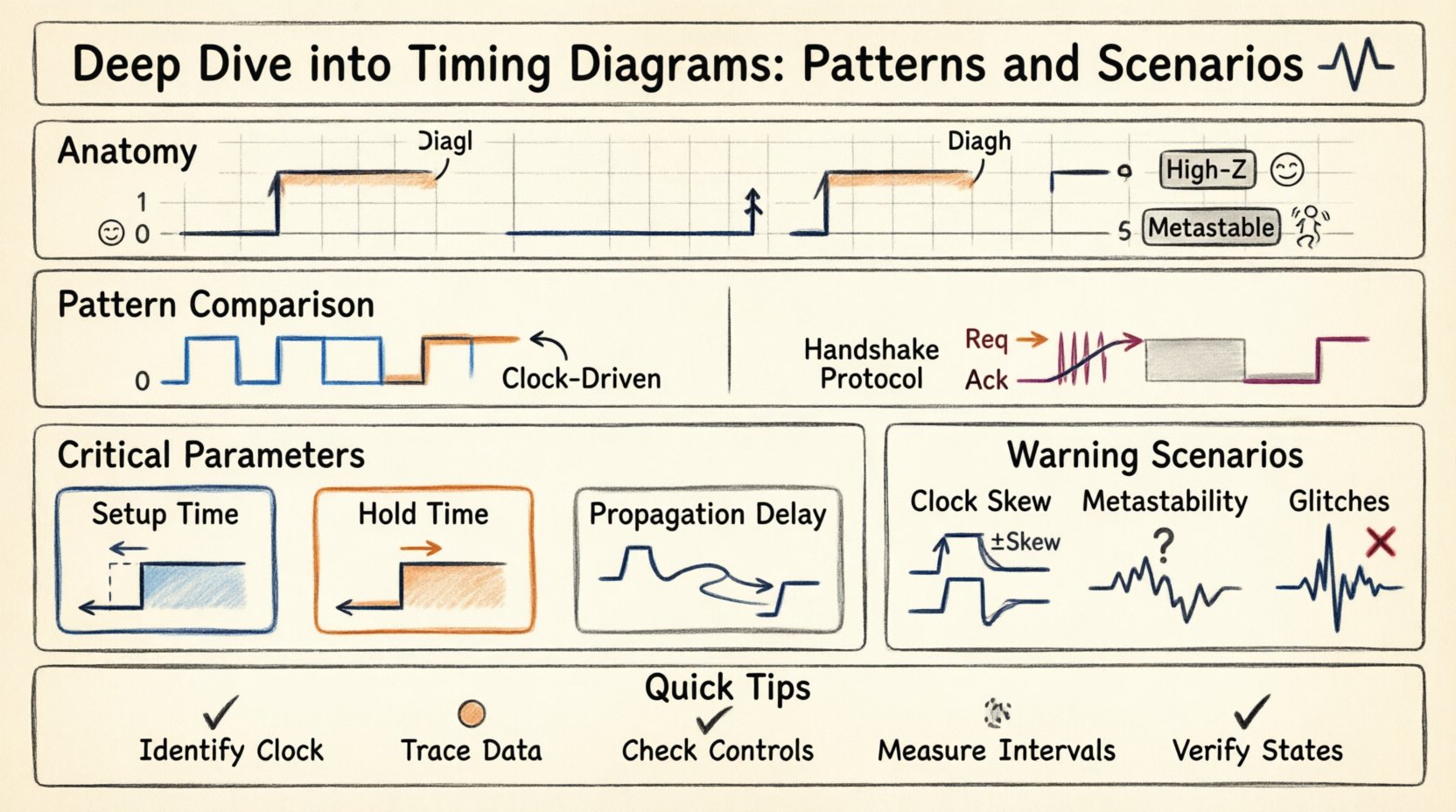

📐 Anatomia de um Diagrama de Tempo

Um diagrama de tempo é uma representação gráfica em que o eixo horizontal representa o tempo e o eixo vertical representa os níveis dos sinais. Cada linha horizontal corresponde a um sinal ou rede específico no projeto. Compreender os componentes é o primeiro passo para uma análise precisa.

- Eixo do Tempo:Normalmente corre horizontalmente da esquerda para a direita. Pode ser linear ou logarítmico, dependendo da escala dos eventos observados.

- Linhas de Sinal:Traços individuais que representam níveis de tensão. Tensão alta geralmente indica lógica 1, enquanto tensão baixa indica lógica 0.

- Transições:Linhas verticais que indicam uma mudança de estado, como uma borda ascendente (0 para 1) ou descendente (1 para 0).

- Rótulos:Anotações de texto que identificam sinais específicos, pinos ou linhas de controle.

- Marcadores:Linhas verticais tracejadas frequentemente usadas para indicar eventos específicos, como um pulso de clock ou um disparador de reinicialização.

🔢 Níveis e Estados Lógicos

Sinais digitais nem sempre existem estritamente em 0 ou 1. Em cenários práticos, os sinais podem existir em estados indefinidos ou em estados de alta impedância. Um diagrama completo deve levar em conta essas variações.

- Nível Lógico Alto (1):O sinal é conduzido a um nível de tensão reconhecido como verdadeiro logicamente.

- Nível Lógico Baixo (0):O sinal é conduzido a um nível de tensão reconhecido como falso logicamente.

- Alto-Z:O sinal é desconectado do driver, efetivamente flutuando. Isso é comum em buffers de três estados.

- Metastável:Um estado em que o sinal não é nem alto nem baixo, ocorrendo frequentemente durante transições assíncronas.

⚙️ Padrões Comuns de Tempo

Projetos seguem padrões previsíveis para garantir a integridade dos dados. Esses padrões definem como os dados se movem em relação aos sinais de controle. Reconhecer esses padrões ajuda na verificação de que um projeto atende às suas especificações.

📌 Transferência Síncrona de Dados

Projetos síncronos dependem de um sinal de clock global para coordenar ações. Os dados são amostrados apenas em momentos específicos, geralmente na borda ascendente ou descendente do clock.

- Controlado por Clock: Todas as mudanças de estado ocorrem em relação à borda do clock.

- Validade dos Dados: Os dados devem ser estáveis antes da borda do clock e permanecer estáveis após ela.

- Propagação: Há um atraso entre a borda do clock e a mudança na saída.

📌 Handshake Assíncrono

A comunicação assíncrona não depende de um clock compartilhado. Em vez disso, utiliza sinais de controle para indicar quando os dados estão prontos e quando foram recebidos.

- Solicitação (Req): O remetente sinaliza que os dados estão disponíveis.

- Confirmação (Ack): O receptor sinaliza que os dados foram aceitos.

- Estados de Espera: O remetente pode pausar até que o receptor esteja pronto.

| Recursos | Padrão Síncrono | Padrão Assíncrono |

|---|---|---|

| Coordenação | Sinal de Clock Global | Sinais de Handshake de Controle |

| Velocidade | Geralmente Maior | Variável, dependente da resposta |

| Complexidade | Rede de Distribuição de Clock | Lógica de Protocolo |

| Latência | Previsível | Variável |

⏱️ Parâmetros Críticos de Temporização

Além das linhas visuais, restrições numéricas específicas definem se um circuito funcionará corretamente. Esses parâmetros são críticos para a análise de temporização estática e devem ser verificados em relação aos limites físicos.

🛑 Tempo de Setup

O tempo de setup é o tempo mínimo durante o qual o sinal de dados deve permanecer estável antes da borda do clock. Se os dados mudarem muito perto da borda do clock, o flip-flop receptor pode não capturar o valor correto.

- Medição:Medido a partir da borda ativa do clock em direção ao passado.

- Risco:A violação leva à captura incorreta dos dados.

- Requisito:O atraso na trajetória de dados deve ser suficientemente longo para atender à janela de setup.

🛑 Tempo de Hold

O tempo de hold é o tempo mínimo durante o qual o sinal de dados deve permanecer estável após a borda do clock. Isso garante que o latch tenha tempo suficiente para fixar o valor de entrada.

- Medição:Medido a partir da borda ativa do clock em direção ao futuro.

- Risco:A violação leva à metastabilidade ou à captura de dados incorretos.

- Requisito:O atraso na trajetória de dados deve ser suficientemente curto para permitir a janela de hold.

⚡ Atraso de Propagação

Este é o tempo necessário para um sinal percorrer da entrada de uma porta lógica até sua saída. Ele varia com base na capacitância de carga e na resistência interna do transistor.

- tpd (Alto para Baixo):Tempo para transição de 1 para 0.

- tpd (Baixo para Alto):Tempo para transição de 0 para 1.

- Skew:Diferenças no atraso entre caminhos paralelos.

🚨 Cenários Críticos de Temporização

Certos cenários apresentam desafios significativos que exigem análise cuidadosa. Essas situações frequentemente envolvem interações entre diferentes domínios de clock ou limitações físicas do hardware.

🔄 Atraso de Relógio

O atraso de relógio ocorre quando o sinal de relógio chega em componentes diferentes em tempos diferentes. Isso pode acontecer devido a diferenças na rotação ou à distância física.

- Atraso Positivo: O relógio de destino chega mais tarde que o relógio de origem.

- Atraso Negativo: O relógio de destino chega antes que o relógio de origem.

- Impacto: Pode reduzir efetivamente as margens de tempo de setup ou aumentar as violações de tempo de hold.

🌊 Metestabilidade

A metestabilidade é um estado em que a saída de um flip-flop não é nem alta nem baixa. Ela geralmente ocorre quando os tempos de setup ou hold são violados, especialmente em transições assíncronas.

- Resolução: O circuito eventualmente se resolve em um estado estável, mas o tempo necessário é imprevisível.

- Solução: Use sincronizadores (flip-flops de múltias etapas) para reduzir a probabilidade de falha.

- MTBF: O Tempo Médio Entre Falhas é calculado com base nas taxas de resolução de metestabilidade.

📉 Atravessamentos

Atravessamentos são picos de curta duração no sinal que podem ser confundidos com transições válidas. Eles ocorrem frequentemente devido a diferenças nos atrasos de propagação em caminhos diferentes.

- Causas: Comprimentos de caminho desiguais ou condições de corrida.

- Efeito: Pode acionar mudanças de estado não desejadas na lógica posterior.

- Mitigação: Use lógica de filtragem ou garanta o fechamento adequado do tempo.

🔍 Análise de Ondas

Ao revisar um diagrama de tempo, uma abordagem sistemática garante que nenhum detalhe seja ignorado. Os engenheiros devem rastrear o fluxo de sinais de dados e de controle para identificar discrepâncias.

🔍 Análise Passo a Passo

- Identifique o Relógio: Localize o sinal principal de relógio. Determine se ele é acionado pela borda de subida ou de descida.

- Rastreie os Caminhos de Dados: Siga as linhas de dados da fonte até o destino.

- Verifique os sinais de controle: Verifique se os habilitadores, reinícios e limpezas são ativados corretamente.

- Meça os intervalos: Calcule o tempo entre eventos específicos para verificar os requisitos de setup e hold.

- Verifique as transições de estado: Certifique-se de que o estado de saída corresponde à função lógica esperada.

🔍 Leitura de Disparos por Borda

Compreender como um componente reage às bordas do sinal é fundamental.

- Disparado por Borda Positiva: A ação ocorre na transição de baixo para alto.

- Disparado por Borda Negativa: A ação ocorre na transição de alto para baixo.

- Disparado por Nível: A ação ocorre enquanto o sinal permanece em um nível específico.

🛠️ Padrões de Documentação

Documentação clara garante que os projetos sejam compreendidos por outros engenheiros. A consistência na notação e rotulagem evita mal-entendidos durante a depuração ou transferência.

📝 Convenções de Rotulagem

- Nomes de Sinais: Use convenções de nomeação consistentes (por exemplo,

clk,rst_n,data_in). - Polaridade: Indique claramente os sinais ativos baixo, geralmente com uma barra ou sufixo.

- Unidades: Indique claramente as unidades de tempo (ns, µs, ms) no eixo do tempo.

- Escala: Certifique-se de que a escala de tempo seja adequada para os eventos mostrados.

📝 Clareza Visual

- Espaçamento:Evite linhas sobrepostas sempre que possível.

- Contraste:Use cores distintas ou espessuras de linha para diferentes tipos de sinal.

- Anotações:Adicione notas explicando comportamentos complexos ou restrições específicas.

- Grade:Use um fundo de grade para auxiliar na medição de intervalos de tempo.

🚧 Fluxo de Solução de Problemas

Quando um projeto não atende aos requisitos de tempo, um processo estruturado de solução de problemas ajuda a identificar a causa raiz. Isso envolve examinar o diagrama em relação às restrições físicas.

🚧 Identificando Violações

- Verifique o Tempo de Setup:Os dados estão chegando muito tarde em relação ao clock?

- Verifique o Tempo de Manutenção:Os dados estão mudando muito cedo após o clock?

- Verifique a Frequência do Clock:O período do clock é menor que o mínimo exigido?

🚧 Estratégias de Mitigação

- Registradores de Pipelining:Insira registradores adicionais para quebrar caminhos combinacionais longos.

- Gating de Clock:Reduza a atividade para diminuir o consumo de energia e potencialmente melhorar o tempo.

- Inserção de Buffers:Adicione buffers para equilibrar os atrasos em caminhos paralelos.

- Restrições de Tempo:Defina caminhos falsos para excluir lógica que não afeta o fluxo de dados.

📈 Melhores Práticas para o Projeto

Adotar práticas recomendadas durante a fase de design reduz a probabilidade de problemas de tempo mais tarde no ciclo de desenvolvimento. Planejamento proativo é mais eficiente do que correção reativa.

- Padronize Interfaces:Use protocol conhecidos para transferência de dados para simplificar a verificação de tempo.

- Minimize Caminhos Assíncronos:Mantenha as interações assíncronas ao mínimo para reduzir os riscos de metastabilidade.

- Documente Suposições:Indique claramente as frequências do clock e os níveis de tensão nas especificações do design.

- Revise Regularmente:Realize revisões de tempo em cada marco principal do projeto.

🎯 Resumo dos Conceitos Principais

Diagramas de tempo são ferramentas essenciais para visualizar o comportamento temporal de sistemas digitais. Eles revelam como os sinais de dados e de controle interagem ao longo do tempo, destacando restrições críticas como tempos de setup e hold. Ao compreender a anatomia desses diagramas, engenheiros conseguem identificar padrões, prever erros e garantir um desempenho robusto do sistema.

Os principais aprendizados incluem a distinção entre padrões síncronos e assíncronos, a importância da gestão do desvio de clock e a necessidade de padrões claros de documentação. Seguir esses princípios facilita o design confiável e simplifica o processo de verificação.

A análise contínua dos dados de onda garante que os designs permaneçam dentro dos limites operacionais. À medida que a tecnologia avança e as velocidades do clock aumentam, a precisão exigida na análise de tempo torna-se ainda mais crítica. O domínio desses conceitos permite a criação de arquiteturas digitais estáveis e de alto desempenho.