Diagramas de tempo são a base do design de sistemas digitais. Eles fornecem uma linguagem visual que engenheiros usam para descrever como os sinais mudam ao longo do tempo. Seja você que está projetando uma interface de microcontrolador ou depurando um protocolo de comunicação, entender esses diagramas é essencial. Este guia percorre o processo de criação e interpretação desses diagramas sem complexidade desnecessária.

Começar pode parecer assustador, mas com o framework certo, você pode desenhar diagramas eficazes rapidamente. Abordaremos os componentes principais, a lógica por trás das transições de sinal e os parâmetros críticos que definem a confiabilidade do sistema. Vamos mergulhar na mecânica do tempo dos sinais.

Compreendendo a Finalidade Central 🧠

Um diagrama de tempo é uma representação gráfica da sequência de eventos em um sistema. Ele mapeia o estado dos sinais contra um eixo comum do tempo. Diferentemente dos diagramas esquemáticos que mostram conexões físicas, os diagramas de tempo focam nas relações temporais. Essa distinção é crucial para depurar erros lógicos que não aparecem na análise estática do circuito.

Quando você desenha esses diagramas, está documentando o comportamento dos sinais de dados e de controle. O objetivo é garantir que um sinal esteja pronto antes que outro atue sobre ele. Essa sincronização evita a corrupção de dados e garante uma operação estável.

-

Clareza Visual: Eles tornam dependências temporais abstratas concretas.

-

Apoio à Depuração: Eles destacam condições de corrida e violações de configuração.

-

Documentação: Eles servem como referência para equipes de hardware e software.

-

Verificação: Eles ajudam a validar que a lógica corresponde à especificação.

Sem um diagrama claro, é fácil ignorar problemas sutis de tempo que só ocorrem sob condições específicas. Padronizando a forma como você desenha, reduz a ambiguidade para todos os envolvidos no projeto.

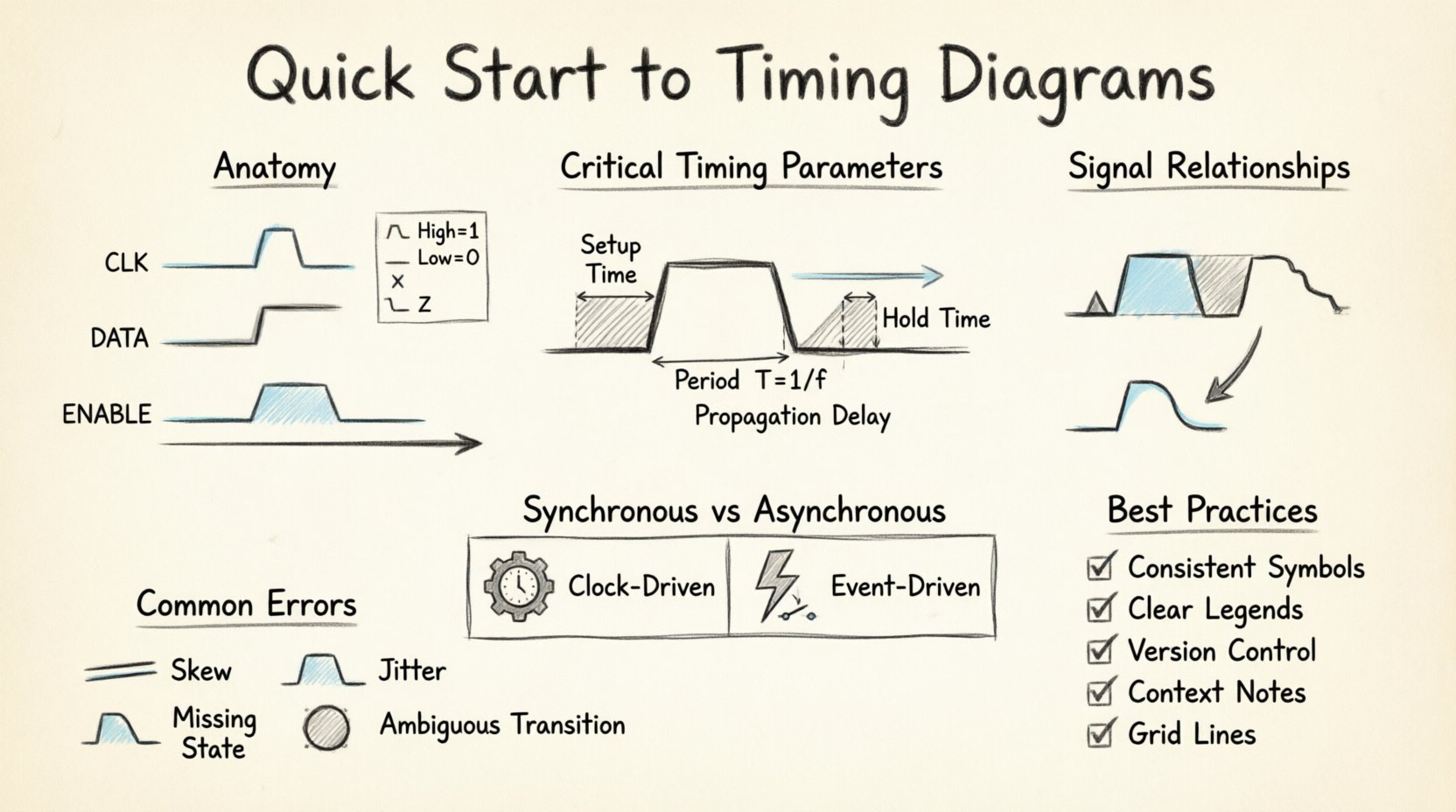

Anatomia de um Diagrama de Tempo 📐

Todo diagrama de tempo compartilha uma estrutura comum. Dominar essa estrutura permite que você leia formas de onda complexas com facilidade. A disposição é consistente em diferentes áreas da engenharia, desde sistemas embarcados até redes de alta velocidade.

1. O Eixo do Tempo ⏰

O eixo horizontal representa o tempo. Ele flui da esquerda para a direita. O tempo nem sempre é linear em todos os contextos, mas na maioria dos diagramas padrão, distâncias iguais representam intervalos de tempo iguais. Você não precisa rotular cada milissegundo, mas marcar intervalos-chave ajuda a escalar as informações.

-

Direção:Sempre da esquerda para a direita.

-

Escala:Pode ser linear ou logarítmica, dependendo da frequência do sinal.

-

Marcadores:Use linhas verticais para indicar eventos específicos, como bordas de clock.

2. As Linhas de Sinal 📊

Os sinais são representados por linhas horizontais empilhadas verticalmente. Cada linha corresponde a um fio ou rede específica no circuito. O nome do sinal geralmente aparece no lado esquerdo ou direito da linha.

-

Agrupamento:Sinais relacionados, como linhas de endereço e dados, são frequentemente agrupados juntos.

-

Rotulagem:Sempre rotule os sinais claramente para evitar confusão entre nomes semelhantes.

-

Ordem:Coloque o sinal mais importante no topo ou na parte inferior, dependendo da convenção.

3. Níveis Lógicos 🔋

Os sinais alternam entre estados definidos. Na lógica digital, esses são geralmente Alto e Baixo, ou 1 e 0. A posição vertical da linha indica o estado.

|

Estado |

Notação Comum |

Significado Físico |

|---|---|---|

|

Alto |

1, H, VCC |

Tensão positiva |

|

Baixo |

0, L, GND |

Terra ou tensão zero |

|

Desconhecido |

X |

Estado indeterminado |

|

Alta Impedância |

Z |

Desconectado ou flutuante |

Compreender esses níveis é o primeiro passo para ler o diagrama. As transições entre esses níveis são onde acontece a ação.

Parâmetros Críticos de Temporização ⚙️

Temporização não é apenas sobre desenhar linhas; é sobre definir restrições. Certos parâmetros determinam quão rápido um sinal pode mudar e quando ele deve estar estável. Essas restrições são vitais para garantir que o sistema funcione corretamente.

1. Tempo de Setup ⏳

O tempo de setup é a quantidade mínima de tempo em que um sinal de dados deve permanecer estável antes da chegada de um flanco de clock. Se os dados mudarem muito perto do flanco de clock, o sistema pode capturar um valor incorreto. Essa é uma restrição crítica em sistemas síncronos.

-

Definição:Tempo antes do flanco ativo do clock.

-

Violação:Causa metastabilidade ou captura incorreta de dados.

-

Regra de Projeto: Certifique-se de que os dados estejam estáveis bem antes do acionamento do clock.

2. Tempo de Manutenção ⏳

O tempo de manutenção é o tempo mínimo durante o qual um sinal de dados deve permanecer estável após o borda do clock. Se o sinal mudar muito cedo após o acionamento, o elemento receptor pode não capturar o valor corretamente.

-

Definição:Tempo após a borda ativa do clock.

-

Violação: Semelhante ao tempo de preparação, causa erros de dados.

-

Regra de Projeto: Certifique-se de que o sinal não mude imediatamente após o clock.

3. Atraso de Propagação ⏱️

O atraso de propagação é o tempo necessário para que um sinal percorra do entrada de um componente até sua saída. Nenhum componente eletrônico é instantâneo. Esse atraso se acumula em múltias etapas e deve ser considerado em projetos de alta velocidade.

-

Fonte:Atrasos internos das portas e comprimento dos fios.

-

Impacto: Limita a frequência máxima de operação.

-

Medição:Medido do ponto de 50% da entrada até o ponto de 50% da saída.

4. Período e Frequência 🔁

Para sinais de clock, o período é o tempo entre dois pontos idênticos consecutivos na onda (por exemplo, borda ascendente até borda ascendente). A frequência é o inverso do período.

-

Período: T = 1 / f

-

Ciclo de Trabalho:Porcentagem de tempo em que o sinal está alto dentro de um período.

-

Estabilidade:O jitter do clock afeta a precisão do tempo.

Leitura e Análise de Relacionamentos de Sinais 🔄

Uma vez que você entenda os componentes, o próximo passo é analisar como os sinais interagem. É aqui que o diagrama se torna uma ferramenta diagnóstica. Você procura dependências e conflitos potenciais.

1. Acionamento por Borda 📉

A maioria dos circuitos digitais é acionada por bordas específicas do clock. Alguns são acionados pela borda ascendente, enquanto outros usam a borda descendente. Você deve identificar qual borda é ativa para cada componente do seu sistema.

-

Borda Ascendente: Transição de Baixo para Alto.

-

Aresta de Queda: Transição de Alto para Baixo.

-

Ambas as Arestas: Alguns sistemas amostram dados em ambas as transições.

Ao desenhar, use pequenos triângulos ou entalhes para indicar qual aresta está ativa. Isso evita confusão durante a implementação.

2. Janelas de Dados Válidos 🕒

Os dados são válidos apenas dentro de uma janela específica. Antes do tempo de setup e após o tempo de hold, a linha de dados não deve mudar. Fora dessa janela, os dados são considerados válidos. Marcar essa janela no seu diagrama esclarece as expectativas.

-

Janela: Definida por Setup + Hold + Atraso de Propagação.

-

Violação: Se os dados mudarem fora dessa janela, ocorrem erros.

-

Dica Visual: Use regiões sombreadas para destacar os períodos de dados válidos.

3. Sinais Assíncronos 📡

Nem todos os sinais seguem o clock. Sinais assíncronos como interrupções ou reinicializações operam de forma independente. Eles exigem um manuseio cuidadoso nos diagramas de tempo para mostrar sua prioridade e latência.

-

Prioridade: Interrupções frequentemente têm precedência sobre os ciclos de clock.

-

Latência: Observe o atraso entre a afirmação e a resposta.

-

Estabilidade: Certifique-se de que os sinais assíncronos sejam estáveis para os requisitos de setup/hold.

Sistemas Síncronos vs Assíncronos 📡

A diferença entre o design síncrono e assíncrono afeta como você constrói seus diagramas. Cada abordagem tem regras e convenções específicas.

|

Funcionalidade |

Síncrono |

Assíncrono |

|---|---|---|

|

Controle |

Controlado por um clock |

Controlado por eventos |

|

Previsão |

Tempo fácil de prever |

Tempo mais difícil de prever |

|

Complexidade |

Lógica padronizada |

Protocolos de handshake |

|

Potência |

Maior devido ao clock |

Muitas vezes menor |

Em um diagrama síncrono, você verá uma linha de clock dominante que alinha todos os outros sinais. Em um diagrama assíncrono, você verá handshakes e estados de espera. Ambos exigem documentação precisa de tempo.

Erros Comuns e Como Evitá-los ⚠️

Erros em diagramas de tempo podem levar a revisões caras de hardware. Estar ciente dos armadilhas comuns ajuda você a criar representações mais limpas e precisas.

1. Ignorar o Skew 📏

O skew é a diferença no tempo de chegada de um sinal em pontos diferentes. Se você assumir que todos os sinais chegam simultaneamente, pode perder violações de tempo. Sempre considere as diferenças de comprimento de fio e carga.

-

Verifique: Compare os tempos de chegada em receptores diferentes.

-

Correção: Adicione buffers de atraso ou ajuste os comprimentos das trilhas.

-

Visual: Mostre pequenos deslocamentos em linhas paralelas se o skew for significativo.

2. Ignorar o Jitter ⚡

O jitter é a variação no tempo de um sinal. Um clock pode não ser perfeitamente periódico. Em projetos de alta velocidade, o jitter pode reduzir suas margens de tempo. Represente o jitter como uma área sombreada ao redor da borda do clock.

-

Fonte: Ruído na fonte de alimentação ou interferência externa.

-

Impacto: Reduz o tempo efetivo de setup e hold.

-

Visual: Use linhas borradas ou faixas para indicar incerteza.

3. Transições Ambíguas 🔄

Uma transição que parece uma linha reta pode na verdade ser uma inclinação. Sinais reais não mudam instantaneamente. Desenhar linhas verticais perfeitas implica velocidade infinita, o que é fisicamente impossível.

-

Melhor Prática:Desenhe as transições com uma leve inclinação se a precisão for necessária.

-

Convenção:Linhas verticais são aceitáveis para representação lógica.

-

Clareza:Garanta que a intenção seja clara, independentemente da inclinação.

4. Transições de Estado Ausentes 🚦

Máquinas de estado complexas frequentemente têm estados intermediários que não são óbvios. Se você desenhar apenas os estados inicial e final, perderá informações críticas sobre a sequência.

-

Detalhe:Mostre todas as mudanças de estado relevantes.

-

Rótulos:Anote os estados com seus nomes ou valores.

-

Lógica:Garanta que o diagrama reflita o fluxo lógico real.

Melhores Práticas para Documentação 📝

Para garantir que seus diagramas sejam úteis por anos, siga um estilo consistente. Isso os torna mais fáceis de manter e compartilhar com outros engenheiros.

-

Símbolos Consistentes:Use as mesmas pontas de seta e estilos de linha em toda parte.

-

Legendas Claras:Defina quaisquer símbolos personalizados ou abreviações usadas.

-

Controle de Versão:Rotule os diagramas com números de versão e datas.

-

Contexto:Inclua uma breve descrição do sistema sendo diagramado.

-

Linhas de Grade:Use uma grade para ajudar a alinhar os sinais e marcar intervalos de tempo.

A consistência reduz a carga cognitiva de quem lê seu trabalho. Também torna mais fácil identificar anomalias quando você revisar o diagrama posteriormente.

Diagnóstico com Análise de Tempo 🛠️

Quando um sistema falha, os diagramas de tempo são frequentemente o primeiro lugar a ser verificado. Eles ajudam a identificar se o problema é lógico ou temporal.

1. Identificando Condições de Corrida 🏁

Uma condição de corrida ocorre quando a saída depende da ordem dos eventos. Se dois sinais chegarem a uma porta ao mesmo tempo, o resultado pode ser imprevisível. Diagramas de tempo revelam esses sobreposições.

-

Procure por: Sinais cruzando simultaneamente.

-

Resolução: Adicione amortecimento ou reorganize a lógica.

-

Prevenção: Projete com margens para evitar transições simultâneas.

2. Detectando Glitchs ⚡

Glitchs são pulsos curtos que ocorrem devido a atrasos de propagação. Eles podem acionar um flip-flop inadvertidamente. Em um diagrama, aparecem como picos estreitos entre níveis estáveis.

-

Visual: Pulsos estreitos que não correspondem ao período do clock.

-

Correção: Use filtragem ou fixe o sinal na borda estável.

-

Análise: Verifique se a largura do pulso excede o tempo de retenção.

3. Verificando Protocolos de Barramento 📡

Barramentos como I2C ou SPI têm requisitos rigorosos de tempo. As condições de início e fim, o alongamento do clock e os deslocamentos de dados devem estar perfeitamente alinhados. Diagramas de tempo são a forma padrão de verificar esses protocolos.

-

Início/Fim: Verifique a transição correta na linha de dados em relação ao clock.

-

Alongamento: Garanta que o escravo possa manter o clock baixo durante a duração necessária.

-

Dados: Confirme que os dados estejam estáveis durante a fase alta do clock.

Pensamentos Finais sobre Integridade de Sinal 🎯

Criar diagramas de tempo precisos é uma habilidade que melhora com a prática. Exige um entendimento profundo de como os eletrônicos se comportam ao longo do tempo. Ao seguir as orientações acima, você poderá criar diagramas que sejam tanto informativos quanto confiáveis.

Lembre-se de que esses diagramas são ferramentas de comunicação. Eles pontuam a lacuna entre a teoria e a implementação. Quando você desenha um diagrama de tempo, está contando uma história sobre como o sistema se comporta. Torne essa história clara, precisa e consistente.

Concentre-se nos parâmetros essenciais: setup, hold, atraso e skew. Mantenha o layout limpo e as etiquetas sem ambiguidade. Com esses hábitos, você descobrirá que desenhar diagramas de tempo torna-se uma parte natural do seu processo de design, permitindo que você finalize em minutos, em vez de horas.