Compreender o fluxo de sinais dentro de um sistema digital é essencial para engenheiros que trabalham com hardware, firmware ou software embarcado. Um diagrama de temporização serve como a principal ferramenta visual para mapear como diferentes sinais interagem ao longo de um período específico. Essa representação visual permite que equipes verifiquem se os dados são capturados corretamente, se os relógios são estáveis e se as transições lógicas ocorrem sem conflito. Sem uma compreensão precisa desses diagramas, a confiabilidade do sistema pode sofrer significativamente. Este guia explora os elementos essenciais que compõem um diagrama de temporização, garantindo um design e análise precisos.

O que é um Diagrama de Temporização? 📊

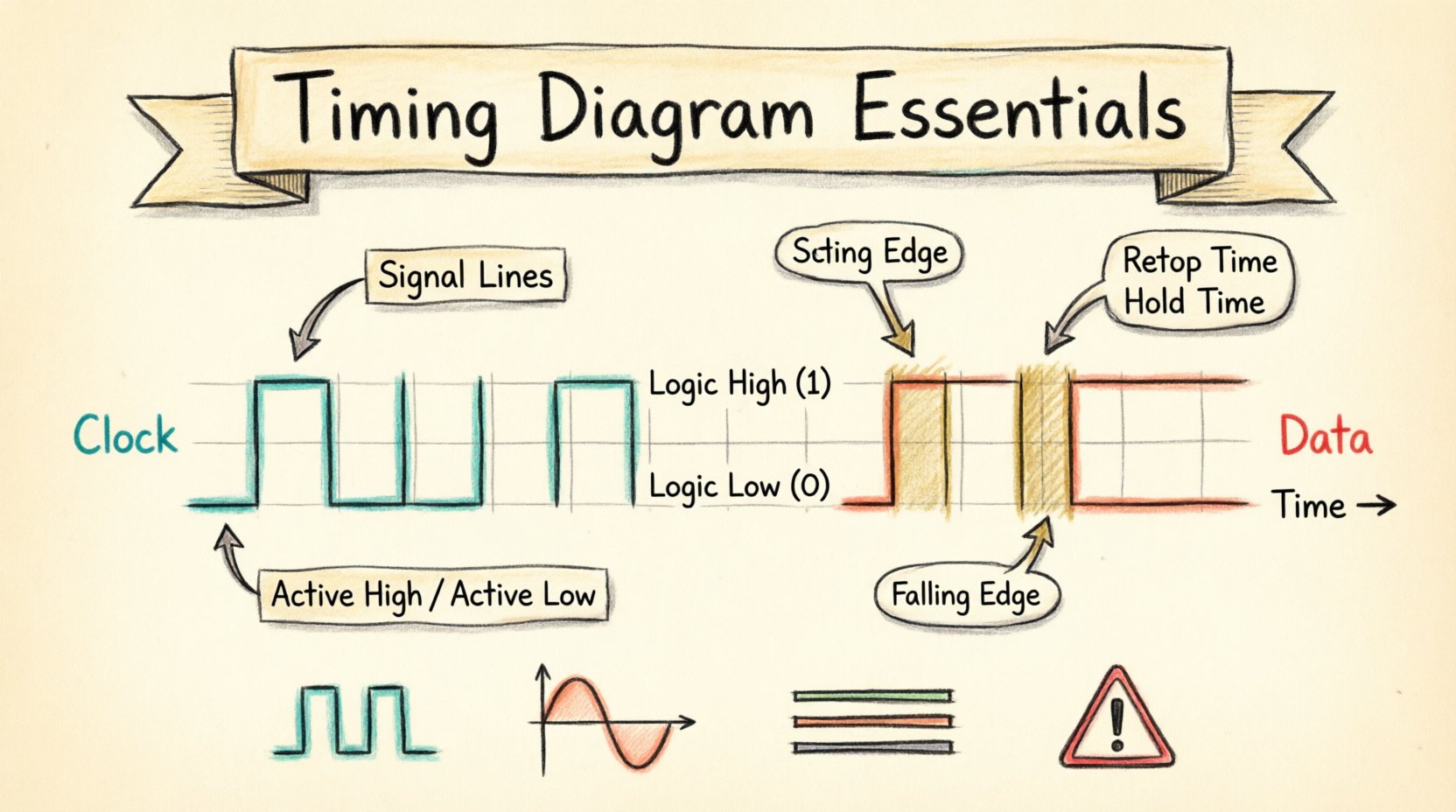

Um diagrama de temporização é uma ilustração gráfica que mostra o comportamento de dois ou mais sinais ao longo do tempo. Ele mapeia a sequência de eventos, indicando quando os sinais mudam de estado, por quanto tempo permanecem nesse estado e como se relacionam com uma fonte de relógio. No design de hardware, esses diagramas são indispensáveis para verificar se os componentes se comunicam corretamente. No software, ajudam a visualizar concorrência, condições de corrida e pontos de sincronização.

Esses diagramas geralmente representam o tempo no eixo horizontal (eixo x) e o nível ou estado do sinal no eixo vertical (eixo y). As linhas verticais representam pontos específicos no tempo, enquanto as linhas horizontais indicam o estado estável de um sinal. As transições entre esses estados são cruciais, pois indicam a transferência real de dados ou ações de controle ocorrendo dentro do sistema.

Componentes Principais de um Diagrama de Temporização 🔧

Para ler ou criar um diagrama de temporização eficaz, é necessário entender os blocos fundamentais. Todo diagrama, independentemente da complexidade, depende de um conjunto consistente de elementos para transmitir informações com precisão.

- Eixo do Tempo: A linha de base horizontal que representa a progressão do tempo. Geralmente flui da esquerda para a direita, indicando do “passado” para o “futuro”.

- Linhas de Sinal: Trilhas horizontais atribuídas a fios específicos, barramentos ou variáveis. Cada linha representa o nível lógico de um sinal específico.

- Níveis Lógicos: As posições verticais na linha de sinal. Normalmente, os estados alto (1, Vcc, Verdadeiro) e baixo (0, Terra, Falso) são mostrados.

- Transições: As linhas verticais que conectam os níveis lógicos. Uma borda ascendente vai do baixo para o alto, enquanto uma borda descendente vai do alto para o baixo.

- Anotações: Rótulos de texto ou marcadores que esclarecem eventos específicos, atrasos ou estados.

O Eixo do Tempo: A Precisão Importa ⏳

O eixo do tempo é a base do diagrama. Ele nem sempre representa segundos no mundo real; muitas vezes, representa ciclos de relógio ou nanossegundos, dependendo da velocidade do projeto. A consistência na escala é vital. Se uma seção do diagrama mostra 10 nanossegundos por quadrado da grade, outra seção deve manter essa escala, a menos que seja explicitamente ampliada para detalhes.

Ao analisar o desempenho do sistema, o eixo do tempo ajuda a identificar gargalos. Por exemplo, se um sinal de dados requer 50 nanossegundos para estabilizar, mas a borda do relógio ocorre após 40 nanossegundos, uma violação existe. O eixo permite que engenheiros meçam esses intervalos diretamente.

Linhas de Sinal e Níveis Lógicos 🔄

Cada linha de sinal corresponde a um fio físico ou uma variável lógica. Em sistemas complexos, um barramento pode ser representado por uma linha grossa com múltiplos sinais agrupados, ou linhas individuais para cada bit. Os níveis lógicos definem o estado do sinal:

- Ativo Alto: O sinal é considerado “ligado” ou “verdadeiro” quando a tensão é alta.

- Ativo Baixo: O sinal é considerado “ligado” ou “verdadeiro” quando a tensão é baixa. Isso geralmente é indicado com um círculo no símbolo ou com uma convenção de nomeação específica.

Compreender o estado ativo é crucial para interpretar sinais de controle como “Seleção de Chip” ou “Habilitação de Escrita”. Interpretar incorretamente um sinal ativo-baixo como ativo-alto pode levar a falhas no projeto que são difíceis de depurar.

Transições e Bordas ⚡

As transições ocorrem quando um sinal muda de um nível lógico para outro. Essas mudanças raramente são instantâneas no mundo físico, mas em um diagrama de temporização, são frequentemente desenhadas como linhas verticais para representar o momento ideal da mudança.

- Borda Ascendente: A transição de baixo para alto. Este é frequentemente o ponto de gatilho para lógica síncrona.

- Aresta de Descida: A transição de alto para baixo. Alguns sistemas usam esta aresta para captura de dados.

- Gatilhado por Aresta: Lógica que responde apenas no momento da transição.

- Gatilhado por Nível: Lógica que responde enquanto o sinal permanece em um estado específico.

Sinais do mundo real têm tempos de subida e descida. Uma linha vertical perfeita é uma abstração. Em projetos de alta velocidade, a inclinação da transição importa porque afeta a interferência eletromagnética e a integridade do sinal.

Parâmetros e Restrições de Temporização 📐

Além das linhas visuais, o valor crítico de um diagrama de temporização reside nos parâmetros quantitativos definidos junto aos sinais. Esses parâmetros determinam os limites físicos dentro dos quais o hardware deve operar.

Tempo de Setup e Tempo de Hold ⚙️

Esses são os dois limites mais comuns no projeto de lógica sequencial, especialmente quando os dados estão sendo capturados por um flip-flop na borda de clock.

- Tempo de Setup: A quantidade mínima de tempo em que o sinal de dados deve permanecer estável antes a borda ativa de clock. Se os dados mudarem muito perto da borda de clock, o flip-flop pode não capturar o valor correto.

- Tempo de Hold: A quantidade mínima de tempo em que o sinal de dados deve permanecer estável depois a borda ativa de clock. Se os dados mudarem muito cedo após a borda, a captura pode ser corrompida.

| Parâmetro | Definição | Consequência da Violação |

|---|---|---|

| Tempo de Setup | Tempo em que os dados devem estar estáveis antes da borda de clock | Metastabilidade ou captura incorreta de dados |

| Tempo de Hold | Tempo em que os dados devem estar estáveis após a borda de clock | Metastabilidade ou captura incorreta de dados |

| Atraso de Propagação | Tempo necessário para o sinal percorrer uma porta | Redução do tempo de folga de temporização, frequência máxima mais baixa |

| Clock Skew | Diferença no tempo de chegada do sinal de clock | Redução efetiva da janela de temporização |

Atraso de Propagação ⏱️

O atraso de propagação é o tempo necessário para que uma mudança na entrada afete a saída. Em um diagrama de temporização, isso é visível como a lacuna entre uma borda do clock e a mudança de dados resultante. Esse atraso é causado por limitações físicas, como a capacitância nos fios e a velocidade de comutação dos transistores.

Ao projetar um sistema, a soma dos atrasos de propagação ao longo de um caminho deve ser menor que o período do clock menos o tempo de setup. Se o atraso for muito longo, o sistema não poderá operar na velocidade de clock desejada.

Clock Skew e Jitter 📉

O clock skew refere-se à diferença nos tempos de chegada do sinal de clock em diferentes partes do circuito. Em um diagrama ideal, a linha de clock é vertical e simultânea para todos os componentes. Na realidade, as diferenças de roteamento causam o skew. O skew positivo significa que o clock chega mais tarde no destino, o que pode ajudar com o tempo de setup, mas prejudica o tempo de hold.

O jitter é a variação no tempo dos bordas do sinal. É ruído que faz com que a borda ocorra antes ou depois do esperado. O alto jitter reduz a margem de temporização efetiva, exigindo que o sistema funcione mais devagar para manter a estabilidade.

Tipos de Sinais e Barramentos 📡

Sistemas diferentes utilizam métodos de sinalização diferentes. O diagrama de temporização deve refletir essas diferenças para ser preciso.

Sinais Digitais

A maioria dos diagramas de temporização foca na lógica digital. Esses sinais são binários, alternando entre 0 e 1. A clareza do diagrama depende de marcar claramente os limiares lógicos. Alguns sinais podem ter estados intermediários ou condições de “não importa”, geralmente indicados com uma X.

Sinais Analógicos

Embora menos comuns em diagramas de temporização puramente digitais, sinais analógicos como barramentos de tensão ou saídas de sensores são às vezes incluídos. Eles são representados com linhas inclinadas ou curvas, em vez de passos abruptos, indicando variação contínua em vez de mudanças de estado discretas.

Barramentos e Dados Paralelos

Quando múltiplos bits viajam simultaneamente, eles geralmente são agrupados. Um diagrama de temporização de barramento mostra o estado de todos os bits ao mesmo tempo. É essencial rotular a largura do barramento (por exemplo, 8-bit, 32-bit) e mostrar a janela de dados válidos onde todos os bits estão estáveis simultaneamente.

Lendo um Diagrama de Temporização: Um Guia Passo a Passo 🔍

Interpretar esses diagramas exige uma abordagem sistemática para evitar perder detalhes críticos.

- Identifique o Clock: Localize a referência principal de temporização. Todos os outros eventos devem ser medidos em relação a esta linha.

- Determine a Sensibilidade à Borda: Verifique se o sistema é acionado pela borda crescente ou decrescente do clock.

- Rastreie a Validez dos Dados: Procure o período em que as linhas de dados são estáveis. Este é a “janela válida”.

- Verifique os Sinais de Controle: Identifique linhas de habilitação, reset ou seleção de chip que controlam a transferência de dados.

- Meça os Intervalos: Use o eixo do tempo para medir atrasos, tempos de setup e larguras de pulso.

Violações e Erros Comuns de Temporização ⚠️

Mesmo com planejamento cuidadoso, as violações de temporização ocorrem. Reconhecer os sinais em um diagrama é o primeiro passo para corrigi-las.

- Violação de Setup: Os dados chegam muito tarde para o próximo fronte de clock. A solução geralmente envolve reduzir a velocidade do clock ou otimizar o caminho lógico para reduzir o atraso.

- Violação de Hold: Os dados mudam muito cedo após o fronte de clock. Isso geralmente é mais difícil de corrigir, pois pode exigir adicionar atraso ao caminho de dados ou ao caminho de clock.

- Metastabilidade: Um estado em que a saída de um flip-flop é nem 0 nem 1 por um período indefinido. Isso geralmente acontece quando os tempos de setup ou hold são violados.

- Glitches: Pulso curtos e indesejados causados por condições de corrida na lógica combinacional. Eles podem provocar mudanças de estado falsas se não forem filtrados.

Projeto Assíncrono vs. Síncrono 🔄

Diagramas de temporização têm aparência diferente dependendo da metodologia de projeto.

Projeto Síncrono

Eventos são coordenados por um clock global. O diagrama de temporização mostra linhas de clock claras e periódicas. Os dados mudam apenas nos frontes de clock. Essa abordagem simplifica a análise porque a janela de temporização é fixa.

Projeto Assíncrono

Eventos são coordenados por sinais de handshake (como Request e Acknowledge). O diagrama de temporização mostra intervalos irregulares entre eventos. Embora mais flexível, esses diagramas são mais difíceis de analisar porque não há uma referência de tempo fixa.

Aplicação em Protocolos 📡

Protocolos de comunicação dependem fortemente de temporização precisa. Compreender o diagrama é essencial para implementar esses padrões.

Comunicação Serial

Interfaces seriais enviam dados um bit de cada vez. O diagrama de temporização mostra o período do bit. A relação entre o clock e a linha de dados (por exemplo, dados válidos no fronte crescente) define as regras do protocolo.

Comunicação Paralela

Interfaces paralelas enviam múltiplos bits de uma vez. O diagrama de temporização deve mostrar o tempo de setup para toda a barramento. Todos os bits devem estar estáveis antes do ocorrer o fronte de latch.

Melhores Práticas para Documentação 📝

Criar documentação clara garante que outros engenheiros possam entender o sistema sem ambiguidade.

- Use Rótulos Consistentes: Nomeie os sinais exatamente como aparecem no código ou no esquemático.

- Inclua Unidades: Sempre especifique as unidades de tempo (ns, µs, ciclos) no eixo.

- Destaque os Caminhos Críticos: Use linhas em negrito ou cores para indicar os sinais mais sensíveis ao tempo.

- Anote as Violacões: Se uma violação for conhecida, marque-a claramente em vez de escondê-la.

- Mantenha-o Atualizado: Atualize os diagramas sempre que o projeto mudar. Diagramas desatualizados são uma fonte principal de erros.

Considerações Avançadas: Domínios de Relógio Múltiplos 🌐

Sistemas modernos frequentemente operam com múltiplos domínios de relógio funcionando em velocidades diferentes. Um diagrama de tempo para esses sistemas deve mostrar claramente a relação entre os relógios.

- Transições entre Domínios de Relógio: Dados que se movem de um domínio rápido para um domínio lento exigem uma sincronização cuidadosa para evitar perda de dados.

- Relações de Fase: Se dois relógios compartilham uma fonte, mas têm fases diferentes, o diagrama deve mostrar o deslocamento de fase.

- Lógica de Handshake: Pontes assíncronas entre domínios dependem de sinais de handshake. O diagrama de tempo deve mostrar todo o ciclo de solicitação-confirmação.

O Papel da Simulação na Análise de Tempo 💻

Antes da construção do hardware, simulações verificam os diagramas de tempo. Engenheiros usam visualizadores de ondas para comparar o comportamento esperado com os resultados simulados.

- Análise de Tempo Estático: Calcula atrasos no pior caso sem simular ondas reais.

- Simulação de Tempo Dinâmico: Executa uma versão virtual do circuito para gerar ondas reais.

- Simulação Pós-Layout: Leva em conta os comprimentos físicos dos fios e a capacitância após o chip ser projetado.

Essas ferramentas permitem que engenheiros validem o diagrama de tempo contra a realidade física. Se a simulação mostrar uma violação de configuração, o projeto deve ser revisado antes da fabricação.

Conclusão sobre a Precisão do Tempo ✅

Dominar a criação e a interpretação de diagramas de tempo é uma habilidade fundamental para profissionais técnicos. Esses diagramas pontuam a lacuna entre a lógica abstrata e a realidade física. Eles garantem que os sinais cheguem quando necessários, no estado correto e com estabilidade suficiente para o sistema funcionar. Ao seguir os elementos e restrições descritos neste guia, as equipes podem reduzir erros e melhorar a confiabilidade do sistema. A atenção aos detalhes nessas representações visuais traz dividendos na estabilidade e no desempenho do produto final.

Independentemente de trabalhar com interfaces de memória de alta velocidade, microcontroladores de baixo consumo ou barramentos de dados complexos, os princípios permanecem os mesmos. O tempo é a constante, e os sinais são as variáveis. Compreender sua relação é a chave para uma engenharia bem-sucedida.