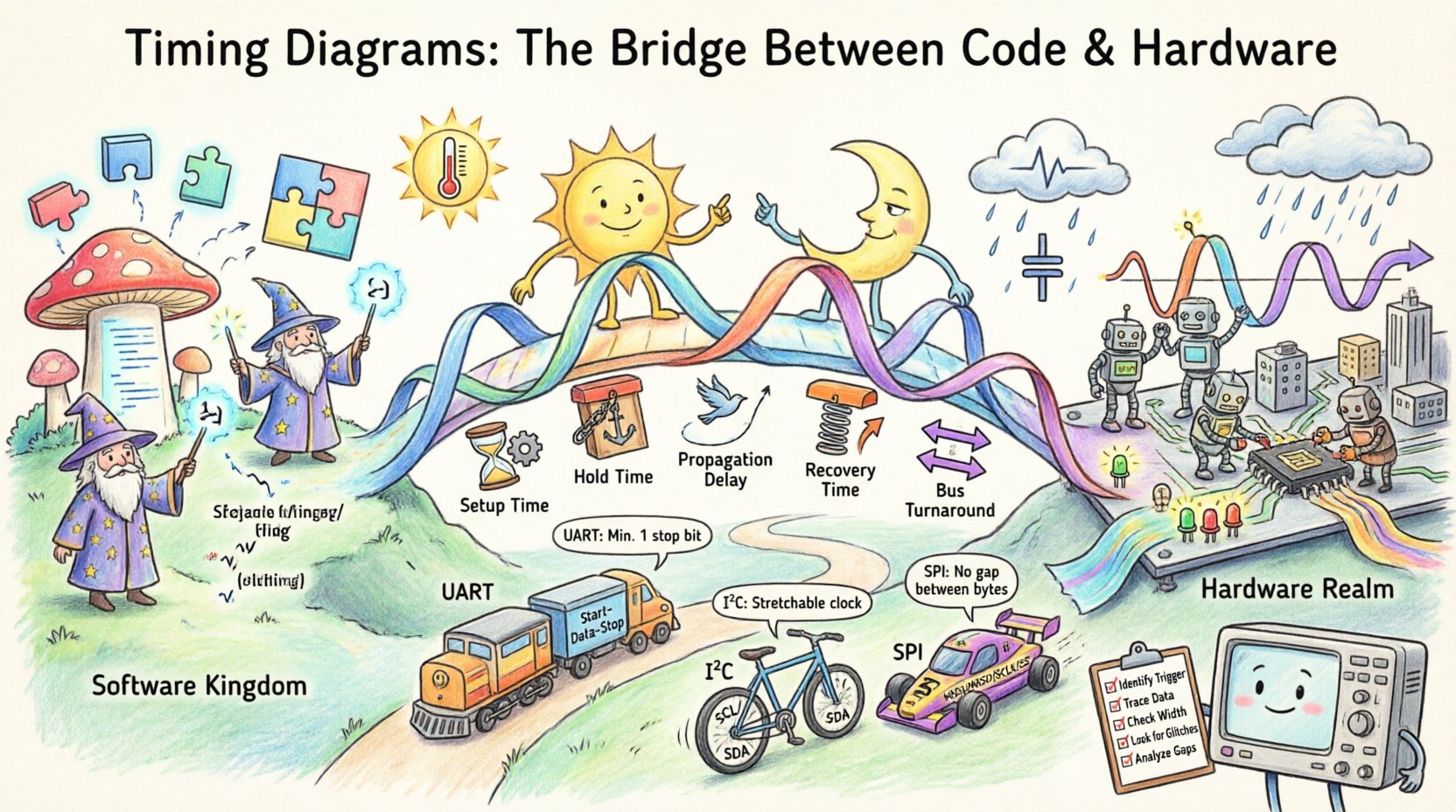

Quando engenheiros de software escrevem código, pensam em instruções, variáveis e fluxos lógicos. Quando engenheiros de hardware projetam circuitos, pensam em níveis de tensão, atrasos de propagação e ciclos de clock. Esses dois mundos muitas vezes existem em um estado de atrito. O código espera que um sinal chegue em um momento lógico específico, mas o hardware opera no tempo físico, sujeito a ruídos, temperatura e resistência elétrica. A ponte entre esses dois domínios é o diagrama de tempo.

Um diagrama de tempo não é meramente uma imagem; é um contrato. Ele define a relação precisa entre eventos no tempo. Ele informa ao firmware quando é seguro ler um pino e informa ao silício quando é seguro acionar uma linha. Sem uma compreensão clara desses diagramas, sistemas embarcados falham de forma imprevisível. Corrupção de dados, condições de corrida e travamentos do sistema tornam-se problemas comuns. Este guia explora a mecânica dos diagramas de tempo, a física por trás deles e como lê-los e criá-los de forma eficaz.

📊 A Anatomia de um Sinal

Na sua essência, a lógica digital depende de estados binários. No mundo físico, no entanto, esses estados são representados por níveis de tensão. Um ‘Alto’ pode ser 3,3 volts, e um ‘Baixo’ pode ser 0 volts. Mas os sinais não mudam instantaneamente. Eles sobem e descem ao longo de um período finito. Um diagrama de tempo visualiza essa transição.

Compreender a linguagem visual desses diagramas é o primeiro passo rumo à maestria. Os elementos principais incluem:

- Eixo do Tempo: Geralmente horizontal, movendo da esquerda para a direita. Pode ser linear ou logarítmico, embora o linear seja o padrão na maioria das análises lógicas.

- Linhas de Sinal: Linhas verticais que representam fios específicos, pinos ou nós internos.

- Transições: O movimento de Baixo para Alto (borda de subida) ou Alto para Baixo (borda de descida). Essas bordas frequentemente acionam mudanças de estado na lógica sequencial.

- Níveis: O estado estável de um sinal antes ou após uma transição.

- Rótulos: Anotações de texto que esclarecem o significado de um pulso ou intervalo específico.

Considere um sinal de clock simples. Ele oscila entre Alto e Baixo. O tempo necessário para completar um ciclo completo é o período. O inverso do período é a frequência. Em um diagrama de tempo, o clock atua como o coração do sistema. Todos os outros sinais geralmente são sincronizados com essas bordas.

🕰️ O Domínio do Clock

A maioria dos sistemas digitais opera dentro de um domínio de clock. Este é um grupo de circuitos que compartilham a mesma referência de tempo. No entanto, os sinais muitas vezes cruzam entre domínios diferentes. Isso introduz complexidade. Um sinal gerado em um domínio rápido pode chegar muito tarde para um domínio lento, ou muito cedo, causando uma violação de retenção.

Ao analisar o tempo, você deve considerar:

- Clock Skew: A diferença no tempo de chegada do sinal de clock em diferentes componentes. Se o clock chegar ao remetente antes do receptor, as margens de tempo diminuem.

- Deslocamento de Fase: Em alguns sistemas, os sinais não estão alinhados com a borda do clock, mas ocorrem no meio do ciclo.

- Jitter: Variações no tempo de um sinal. O jitter pode ser aleatório ou determinístico. Ele reduz a margem de ruído e torna o diagrama menos previsível.

O código escrito para interagir com hardware assume um clock estável. Se o clock físico se desvia devido a flutuações de temperatura ou tensão, o diagrama de tempo já não corresponde à realidade. É por isso que os diagramas de tempo devem incluir faixas de tolerância ou cenários de pior caso.

⚙️ Parâmetros Críticos de Tempo

Parâmetros específicos definem os limites da integridade do sinal. Esses valores são frequentemente encontrados em folhas de dados, mas são melhor compreendidos no contexto de um diagrama de tempo. A tabela a seguir apresenta os parâmetros mais críticos que os engenheiros devem avaliar.

| Parâmetro | Definição | Impacto no Sistema |

|---|---|---|

| Tempo de Preparação | O tempo mínimo em que os dados devem permanecer estáveisantesa borda do clock. | Se violado, o flip-flop receptor não consegue capturar o valor correto. |

| Tempo de Manutenção | O tempo mínimo em que os dados devem permanecer estáveisdepoisa borda do clock. | Se violado, o flip-flop pode entrar em um estado metastável. |

| Atraso de Propagação | Tempo necessário para um sinal percorrer do entrada para saída. | Os atrasos se acumulam em portas lógicas, potencialmente fazendo perder ciclos de clock. |

| Tempo de Recuperação | Tempo necessário para um sinal de controle retornar ao normal após um evento assíncrono. | Afeta a velocidade com que o sistema se recupera de reinicializações ou interrupções. |

| Tempo de Troca de Sentido da Barramento | Tempo necessário para mudar um barramento do modo de saída para modo de entrada. | Crucial para barramentos bidirecionais como I2C ou 1-Wire. |

Violar esses parâmetros nem sempre causa uma falha imediata. Às vezes, o sistema funciona em 99% dos casos e falha apenas sob condições específicas. É por isso que a análise de tempo é um processo iterativo. Você deve verificar se o diagrama permanece válido sob condições extremas de tensão e temperatura.

👀 Lendo o Diagrama de Onda

Ler um diagrama de tempo exige uma abordagem sistemática. Ao depurar um problema de hardware, não olhe apenas pelos níveis dos sinais. Observe as relações entre os sinais.

Siga estas etapas para analisar uma onda:

- Identifique o Gatilho:Encontre o evento que inicia a sequência. Geralmente é uma borda do clock ou uma interrupção externa.

- Rastreie os Dados:Siga as linhas de dados em relação ao gatilho. Os dados aparecem antes ou depois da borda do clock?

- Verifique a Largura Meça a duração dos pulsos. O sinal “Alto” é suficientemente longo para ser reconhecido pela lógica receptora?

- Procure por glitches: Pulsos espúrios que ocorrem entre estados estáveis. Eles podem ser causados por crosstalk ou falhas na lógica.

- Analise a lacuna: Observe o tempo entre o fim de uma transação e o início da próxima. Há tempo suficiente para o hardware fazer a reinicialização?

Muitas vezes, o problema está na lacuna. Se um microcontrolador terminar de escrever dados em um periférico, pode ser necessário um atraso específico antes de enviar o próximo byte. Se o diagrama mostrar esses bytes um após o outro sem lacuna, o código provavelmente é muito agressivo para o hardware.

🔌 Protocolos Comuns e Temporização

Protocolos de comunicação diferentes impõem diferentes restrições de temporização. Compreender essas restrições é essencial para escrever firmware que comunique de forma confiável.

| Protocolo | Característica Fundamental de Temporização | Modo Comum de Falha |

|---|---|---|

| UART | Bit de início seguido pelos bits de dados e bit de parada. Dependente da taxa de baud. | Erros de bit devido ao desvio de clock entre o remetente e o receptor. |

| I2C | Linhas SCL e SDA. Requer resistores de pull-up. O SDA deve permanecer estável durante o estado alto do SCL. | Problemas de retenção da barramento ou estiramento de clock causando tempo esgotado. |

| SPI | As linhas de clock e dados são separadas. Acionadas por borda (configurações CPOL/CPHA). | Escravos respondendo muito lentamente em comparação com a velocidade do clock mestre. |

| Interrupções de GPIO | Sensibilidade à borda. Requer tempo mínimo de processamento na rotina de serviço de interrupção. | Interrupções perdidas devido à execução longa das rotinas de serviço anteriores. |

Por exemplo, no SPI, o momento da borda do clock em relação à linha de dados determina se os dados são capturados na borda ascendente ou descendente. Se o firmware assume um modo e o hardware está configurado para o outro, os dados serão lidos incorretamente. Um diagrama de temporização esclarece essa relação visualmente, evitando erros de configuração.

🔍 Depuração de Problemas com Temporização

Quando um sistema se comporta de forma errática, a primeira ferramenta a ser usada não é um depurador, mas um diagrama de temporização. A depuração com temporização envolve capturar o comportamento elétrico real e compará-lo com o projeto esperado.

Problemas comuns relacionados à temporização incluem:

- Metastabilidade: Quando um sinal chega a um flip-flop muito perto da borda do clock, a saída torna-se imprevisível. Pode se estabilizar em Alto, Baixo ou permanecer em um estado intermediário por um tempo indeterminado.

- Condições de corrida: Quando o resultado depende do tempo relativo dos eventos. Se dois sinais mudarem simultaneamente, a ordem do processamento importa.

- Integridade de Sinal: Reflexões e oscilações em trilhas longas podem causar transições falsas. O diagrama pode mostrar oscilações onde deveria haver um sinal quadrado limpo.

- Violações de Setup/Hold: Os dados mudam muito perto da borda do clock. Isso geralmente é causado por uma velocidade do clock muito alta para o caminho lógico.

Para resolver esses problemas, pode ser necessário adicionar atrasos no código, alterar a frequência do clock ou ajustar o layout do hardware. O diagrama de tempo fornece as evidências necessárias para fazer essas alterações com confiança.

📝 Melhores Práticas para Documentação

Criar diagramas de tempo para documentação é tão importante quanto lê-los. Um tempo mal documentado leva a pesadelos de manutenção. Engenheiros futuros terão dificuldade para entender por que um atraso específico foi adicionado ao código.

Siga estas diretrizes ao criar seus próprios diagramas:

- Use Símbolos Padrão:Evite ícones personalizados, a menos que estejam definidos em uma legenda. Use a notação padrão de borda ascendente/descendente.

- Rotule Tudo:Não assuma que o leitor sabe o que cada linha representa. Rotule claramente pinos, sinais e estados.

- Inclua Contexto:Mostre o estado dos sinais de controle (como Chip Select ou Enable) ao lado das linhas de dados.

- Especifique Unidades:Sempre indique a escala de tempo. É microssegundos, nanossegundos ou ciclos de clock?

- Destaque os Caminhos Críticos:Use linhas em negrito ou cores diferentes para enfatizar os sinais que determinam a estabilidade do sistema.

- Controle de Versão:Atualize os diagramas quando o hardware ou firmware mudar. Um diagrama desatualizado é uma responsabilidade.

A documentação não deve mostrar apenas o caminho “feliz”. Ela também deve mostrar os estados de erro. Como é o diagrama quando ocorre um tempo esgotado? Como é quando um reset é acionado? Esses cenários são frequentemente onde os maiores bugs se escondem.

🌡️ Fatores Ambientais

Um diagrama de tempo é frequentemente gerado sob condições ideais de laboratório. Ambientes do mundo real raramente são ideais. Temperatura, tensão e interferência eletromagnética afetam todos a propagação do sinal.

Considere os seguintes fatores:

- Temperatura:O desempenho do silício degrada em altas temperaturas. O atraso de propagação aumenta. Um sistema que funciona a 25°C pode falhar a 85°C.

- Tensão:Tensão de alimentação mais baixa aumenta o atraso. Tensão mais alta pode reduzir o atraso, mas aumenta o consumo de energia e o calor.

- Capacitância de Carga:Fios longos adicionam capacitância. Isso reduz a velocidade das subidas e descidas dos sinais, ampliando efetivamente a largura do pulso, mas atrasando a transição.

Um projeto robusto leva em conta essas variações. Ao criar um diagrama de temporização para produção, considere o canto de “pior caso”. Isso significa que o diagrama representa as transições de sinal mais lentas possíveis e os bordos de clock mais rápidos possíveis. Se o sistema funcionar nessas condições, funcionará na maioria dos cenários.

🛠️ Criação e Validação de Diagramas

Embora o desenho manual seja possível, a engenharia moderna depende de ferramentas automatizadas para capturar e validar o tempo. No entanto, os princípios permanecem os mesmos, independentemente da ferramenta utilizada. O objetivo é visualizar o fluxo do tempo.

Ao validar um diagrama:

- Compare com os dados técnicos:Garanta que os valores de temporização no seu diagrama correspondam às especificações do fabricante dos chips utilizados.

- Execute simulações:Use ambientes de simulação para modelar a lógica antes de construir o circuito físico.

- Meça o hardware real:Nada substitui a medição real. Capture os sinais do circuito físico e sobreponha-os ao diagrama de projeto.

- Verifique os margens:Há tempo de folga suficiente entre os sinais? Se a margem for zero, qualquer variação causará uma falha.

A validação é um processo contínuo. À medida que o firmware evolui, os requisitos de temporização podem mudar. Um novo manipulador de interrupção pode introduzir uma demora que faz com que um sinal ultrapasse seu prazo. A verificação contínua garante que a ponte entre código e hardware permaneça sólida.

🔗 A Interseção da Lógica e da Física

Em última análise, um diagrama de temporização representa a interseção da lógica e da física. A lógica determina o que deveria acontecer; a física determina o que realmente acontece. A tarefa do engenheiro é alinhar essas duas realidades.

Ao dominar a interpretação e a criação desses diagramas, você ganha a capacidade de diagnosticar falhas complexas que outros podem ignorar. Deixa de adivinhar por que o sistema trava e começa a ver exatamente onde a restrição de temporização foi violada. Esse nível de compreensão transforma um desenvolvedor em um projetista.

Seja você projetando uma interface de sensor simples ou uma barramento de comunicação de alta velocidade, o diagrama de temporização é sua principal referência. Ele garante que o código que você escreve seja executado no tempo esperado pelo hardware. Ele garante que os sinais que você vê na tela correspondam às tensões nos pinos. É a linguagem da sincronização.

Invista tempo para entender esses diagramas. Trate-os com a mesma seriedade que o código. Em sistemas embarcados, o tempo não é apenas um detalhe; é a base da confiabilidade. Quando o código e o hardware falam a mesma linguagem do tempo, o sistema opera com precisão e estabilidade.