Na paisagem intrincada do design de hardware digital, a clareza é fundamental. Engenheiros e designers dependem de representações visuais para comunicar como os sinais se comportam ao longo do tempo. O diagrama de tempo destaca-se como uma das ferramentas mais críticas para esse propósito. Ele transforma a lógica abstrata em uma linha do tempo visual, revelando a dança entre estados altos e baixos em diversos componentes. No entanto, à medida que os sistemas crescem em complexidade, esses diagramas podem se tornar abrumadores. Este guia explora uma estratégia modular para analisar e decompor diagramas de tempo de forma eficaz, garantindo precisão e confiabilidade na verificação de hardware.

Compreender o fluxo de sinais de dados e de controle é essencial para prevenir falhas funcionais. Seja você projetando uma interface de microcontrolador ou um protocolo de comunicação de alta velocidade, a capacidade de ler e criar esses diagramas diferencia um projeto robusto de um frágil. Ao adotar uma perspectiva estruturada e modular, as equipes conseguem gerenciar a complexidade e reduzir o risco de violações de tempo.

Compreendendo os Fundamentos dos Diagramas de Tempo ⏱️

Um diagrama de tempo é uma representação gráfica de como os sinais mudam de estado ao longo do tempo. Ele representa o tempo no eixo horizontal e os estados dos sinais no eixo vertical. Esse formato visual permite que engenheiros verifiquem a relação entre diferentes sinais dentro de um circuito digital. O objetivo principal é garantir que os dados estejam estáveis e válidos quando forem amostrados pelo componente receptor.

Vários elementos-chave formam a base de qualquer diagrama de tempo:

- Linhas de Sinal:Linhas horizontais representam fios individuais ou barramentos que transportam sinais específicos, como clock, dados ou controle.

- Eixo do Tempo:A progressão horizontal indica a passagem do tempo, geralmente marcada em nanossegundos ou ciclos de clock.

- Níveis Lógicos:Os sinais são tipicamente binários, representados como Alto (1) ou Baixo (0). Às vezes, estados indefinidos ou estados de alta impedância também são mostrados.

- Transições:Linhas verticais indicam o momento em que um sinal muda de um estado para outro, como bordas de subida ou descida.

- Anotações:Rótulos de texto geralmente definem restrições específicas, atrasos ou blocos funcionais dentro do diagrama.

Sem uma compreensão clara desses fundamentos, interpretar interações complexas torna-se difícil. Um diagrama de tempo não é meramente um desenho; é um contrato entre o transmissor e o receptor. Ele estabelece as regras segundo as quais os dados devem viajar para serem processados corretamente.

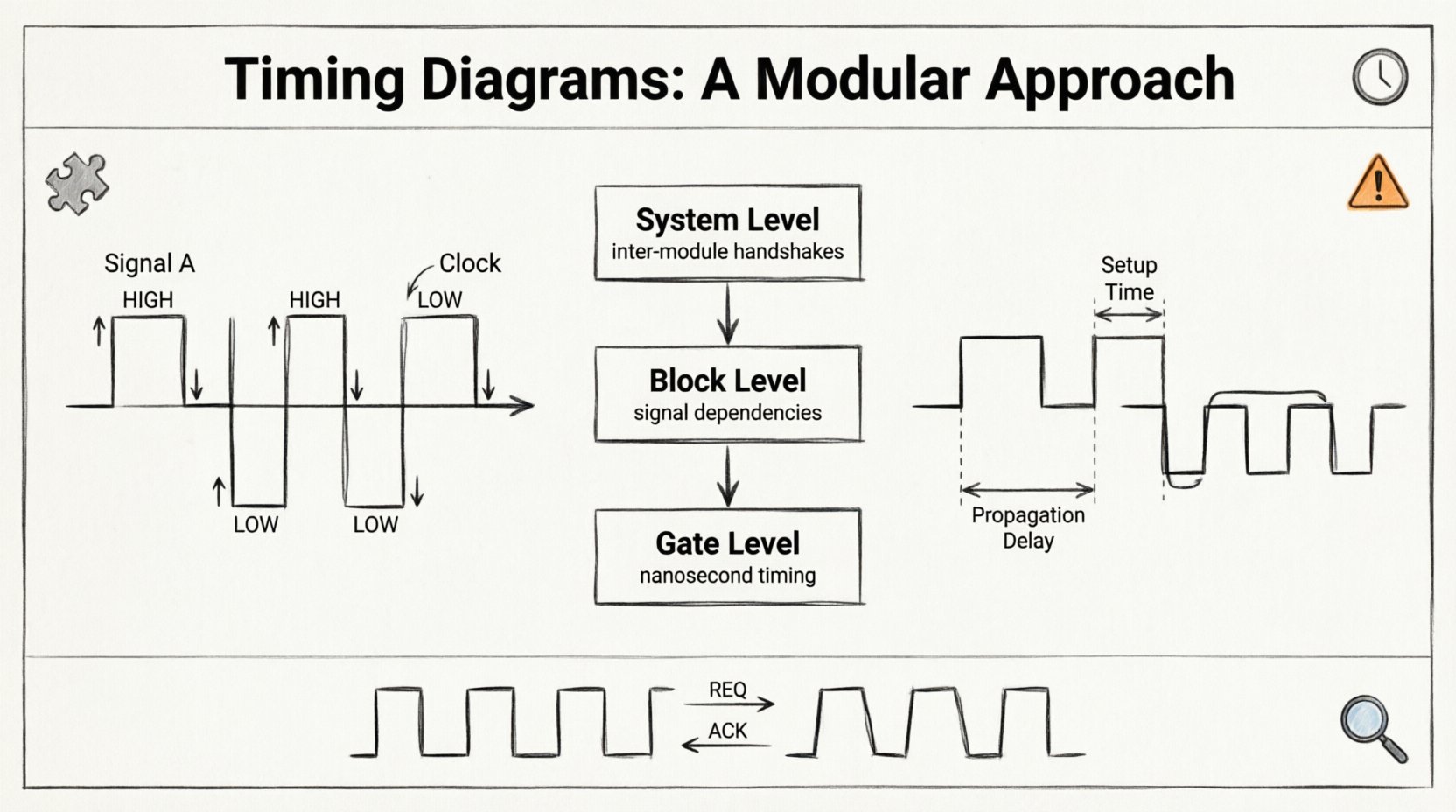

A Estratégia Modular para Projetos Complexos 🧩

Sistemas digitais modernos raramente são simples. Eles consistem em múltiplos subsistemas, cada um com seus próprios requisitos de tempo. Tentar desenhar todo o sistema em um único diagrama frequentemente leva a bagunça e confusão. Uma abordagem modular divide o projeto em partes gerenciáveis. Esse método melhora a legibilidade e simplifica o processo de depuração.

Por que a Modularidade Importa

Dividir um sistema em módulos permite que os designers se concentrem em interfaces específicas sem se perder no ruído da arquitetura inteira. Quando ocorre uma violação de tempo, um diagrama modular torna mais fácil isolar a fonte do problema. Isso reduz a carga cognitiva e facilita a colaboração entre equipes de engenharia diferentes trabalhando em blocos distintos.

Os benefícios dessa abordagem incluem:

- Isolamento de Problemas:Problemas podem ser identificados dentro de um bloco específico, em vez de todo o sistema.

- Reutilização:Padrões de tempo padronizados para módulos comuns podem ser reutilizados em diferentes projetos.

- Escalabilidade:Novas funcionalidades podem ser adicionadas como novos módulos sem redesenhar todo o diagrama.

- Eficiência da Equipe:Equipes diferentes podem trabalhar em seus respectivos diagramas de tempo simultaneamente.

Definindo Fronteiras de Módulo

Para implementar esta estratégia de forma eficaz, devem ser estabelecidas fronteiras claras. Cada módulo deve ter entradas e saídas definidas. O diagrama de tempo de um único módulo deve se concentrar nos sinais que cruzam essa fronteira. Os detalhes internos podem ser abstraídos, a menos que afetem diretamente o tempo de interface.

| Nível de Módulo | Área de Foco | Granularidade de Detalhe |

|---|---|---|

| Nível de Sistema | Comunicação entre módulos | Acenos de alto nível |

| Nível de Bloco | Caminhos internos de dados | Dependências específicas de sinal |

| Nível de Porta | Atrasos de propagação | Tempo exato em nanossegundos |

Organizando os diagramas de acordo com esses níveis, os engenheiros podem manter uma hierarquia clara de informações. Essa estrutura garante que o nível adequado de detalhe esteja disponível na fase apropriada do processo de design.

Decodificando Estados e Transições de Sinais 📊

Uma vez que a estrutura modular esteja em vigor, o próximo passo é analisar os sinais específicos. Nem todos os sinais se comportam da mesma forma. Alguns são contínuos, enquanto outros são disparados por borda. Compreender a natureza de cada sinal é vital para a construção precisa de diagramas.

As categorias comuns de sinais incluem:

- Sinais de Relógio: O batimento cardíaco do sistema. São periódicos e provocam mudanças de estado. Geralmente têm requisitos rigorosos de frequência e ciclo de trabalho.

- Sinais de Dados: A informação real sendo transferida. Devem permanecer estáveis durante janelas específicas em relação ao relógio.

- Sinais de Controle: Sinais que habilitam ou desabilitam funcionalidades, como Chip Select ou Enable.

- Sinais de Reinicialização: Sinais de inicialização que forçam o sistema a entrar em um estado conhecido.

As transições nessas linhas são críticas. Uma borda ascendente geralmente dispara uma ação, enquanto uma borda descendente pode completá-la. Em sistemas assíncronos, a relação entre essas bordas é menos previsível, exigindo uma análise mais detalhada.

Visualizando Atraso de Propagação

Nenhum sinal muda instantaneamente. Limitações físicas causam atraso de propagação. Quando um sinal sai de um componente, leva tempo para viajar pelo fio e chegar ao próximo componente. Os diagramas de tempo devem levar em conta essa latência. Se um diagrama mostra um sinal mudando no tempo T, o ponto receptor pode não vê-lo até T + Δt.

Ignorar o atraso de propagação pode levar a erros significativos na simulação e na implementação. Os engenheiros devem modelar esses atrasos para garantir que os tempos de setup e hold sejam atendidos em toda a trajetória.

Restrições Críticas de Tempo Explicadas ⚠️

A fonte mais comum de falha no projeto digital é a violação de tempo. Essas violações ocorrem quando os sinais não atendem às janelas de estabilidade exigidas. Duas restrições principais regem esse comportamento: tempo de setup e tempo de hold.

Tempo de Setup

O tempo de setup é o tempo mínimo durante o qual os dados devem permanecer estáveis antes da borda ativa do clock. Se os dados chegarem muito tarde, o flip-flop pode não capturar o valor correto. Essa restrição é crítica para determinar a frequência máxima de operação de um sistema. Se o período do clock for menor que a soma do atraso de propagação e o tempo de setup, o sistema falhará.

Principais considerações para o tempo de setup incluem:

- É necessário analisar o caminho mais longo para encontrar o pior cenário possível.

- Variações no processo, na tensão e na temperatura afetam o atraso.

- O jitter do clock pode reduzir a janela de setup disponível.

Tempo de Hold

O tempo de hold é o tempo mínimo durante o qual os dados devem permanecer estáveis após a borda ativa do clock. Se os dados mudarem muito cedo, o flip-flop pode capturar o valor incorreto ou entrar em um estado metastável. Diferentemente do tempo de setup, o tempo de hold é independente da frequência do clock. Ele depende do atraso interno do componente e do caminho externo.

As violações de tempo de hold são frequentemente mais difíceis de corrigir porque não podem ser resolvidas diminuindo a velocidade do clock. Em vez disso, exigem a adição de atraso ao caminho de dados ou a reestruturação da lógica.

Resumo das Restrições de Tempo

| Restrição | Definição | Impacto na Frequência | Método de Resolução |

|---|---|---|---|

| Tempo de Setup | Estável antes da borda do clock | Limita a frequência máxima | Otimizar o caminho lógico |

| Tempo de Hold | Estável após a borda do clock | Independente da frequência | Adicionar atraso de buffer |

| Atraso de Propagação | Tempo para percorrer a lógica | Afeta ambos | Otimização do circuito |

Armadilhas Comuns e Violações 🚫

Mesmo com uma abordagem modular, erros podem surgir. Reconhecer armadilhas comuns ajuda a preveni-los na fase de projeto. Várias tipos de violações são frequentemente encontrados na verificação de hardware.

- Metastabilidade: Ocorre quando um sinal muda exatamente na borda do clock. A saída do flip-flop torna-se imprevisível. Isso é comum ao cruzar domínios de clock.

- Glitches: Pulso curtos e indesejados causados por diferenças nos caminhos lógicos. Isso pode provocar mudanças de estado falsas.

- Clock Skew: Quando o sinal de clock chega em componentes diferentes em tempos diferentes. Isso reduz a janela de tempo efetiva.

- Condições de Corrida: Quando o resultado depende da sequência de eventos, o que é imprevisível em designs assíncronos.

Resolver esses problemas exige uma análise cuidadosa do diagrama de tempo. Procure janelas sobrepostas onde a estabilidade não é garantida. Certifique-se de que as sequências de reset sejam seguidas corretamente para evitar estados indefinidos.

Implementando o Fluxo de Trabalho Modular 🛠️

Para aplicar efetivamente esta metodologia, siga um fluxo de trabalho estruturado. Isso garante que todos os aspectos do tempo sejam cobertos sem redundância.

- Defina Interfaces: Liste claramente todas as entradas e saídas para cada módulo.

- Identifique Domínios de Clock: Determine quais sinais pertencem a qual domínio de clock.

- Mapeie os Caminhos de Dados: Trace o caminho da fonte até o destino.

- Aplique Restrições: Defina os requisitos de setup e hold para cada flip-flop.

- Valide as Transições: Verifique alinhamentos de borda e larguras de pulso.

- Revise a Integração: Certifique-se de que os diagramas de módulo estejam alinhados quando combinados.

Cada etapa se baseia na anterior. Pular uma etapa pode resultar em falhas na cobertura. Por exemplo, ignorar domínios de clock pode causar falhas de sincronização que são difíceis de depurar posteriormente.

Gerenciando Domínios Multi-Clock 🌐

À medida que os designs crescem, frequências de clock múltiplas tornam-se necessárias. Algumas partes do sistema funcionam rápido, enquanto outras funcionam devagar. Sincronizar esses domínios é um dos aspectos mais desafiadores da análise de tempo.

Quando sinais cruzam de um domínio de clock para outro, o diagrama de tempo deve refletir a relação entre os dois clocks. Se os clocks forem assíncronos, é necessário cuidado especial para prevenir a metastabilidade. Técnicas como cadeias de sincronização ou protocolos de handshake são usadas para gerenciar essa transferência de forma segura.

Estratégias-chave para designs multi-clock incluem:

- Codificação Gray: Usando códigos Gray para transmitir contadores de múltiplos bits de forma segura entre domínios.

- Buffers FIFO: Usando filas First-In-First-Out para desacoplar os relógios de leitura e escrita.

- Sinais de handshake: Usando pares Request/Acknowledge para garantir a validade dos dados.

Os diagramas de tempo para esses cenários devem mostrar explicitamente os bordos dos relógios de ambos os domínios. Isso permite que engenheiros verifiquem se os dados permanecem estáveis por tempo suficiente para que o relógio receptor os capture.

Depuração com dados visuais 🔍

Quando um projeto falha, os diagramas de tempo são o primeiro lugar a ser verificado. A depuração exige paciência e uma abordagem sistemática. Comece isolando o módulo com falha. Compare o diagrama esperado com a onda real.

Procure discrepâncias em:

- Temporização do sinal em relação ao relógio.

- Largura do pulso dos sinais de controle.

- Transições de estado durante o reset.

- Glitches nas linhas de dados.

Ferramentas frequentemente oferecem recursos de zoom para inspecionar detalhes em nível de nanossegundo. Use esses recursos para verificar o momento exato em que ocorre uma violação. Correlacione os dados visuais com a lógica para entender a causa raiz.

Pensamentos Finais sobre a Integridade do Projeto 💡

Diagramas de tempo são mais do que simples desenhos técnicos; são o projeto arquitetônico para sistemas digitais confiáveis. Ao adotar uma abordagem modular, engenheiros podem gerenciar a complexidade e manter a clareza. Este método apoia a escalabilidade e reduz a probabilidade de erros custosos.

O sucesso no design de hardware depende da atenção aos detalhes. Cada nanossegundo conta. Cada transição importa. Ao aplicar rigorosamente esses princípios, equipes podem construir sistemas que funcionam de forma previsível em condições do mundo real. A análise modular do tempo garante que nenhum detalhe seja negligenciado, levando a soluções de hardware robustas e eficientes.

A aprimoração contínua dessas habilidades é necessária à medida que a tecnologia avança. Novos padrões e velocidades mais rápidas exigem técnicas de análise atualizadas. Mantenha-se informado sobre as práticas recomendadas emergentes para manter uma vantagem competitiva na área de engenharia digital.